- 18 -

LGE Internal Use Only Copyright © 2010 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3. TECHNICAL BRIEF

3.1.2 Memory support (and LCD interface)

The QSC62x0 device has two external bus interface (EBI) ports: EBI1 and EBI2.

EBI1 supports high-speed synchronous dynamic devices. Its memory controller supports the new mobile

DDR SDRAM memories with its higher bandwidth and ability to run at high clock frequencies. This

interface supports the high-bandwidth, high-density, and low-latency requirements of the QSC’s

advanced on-chip capabilities such as the ARM9 processor, highperformance graphics, and video

applications.

EBI2 is the slower speed interface intended to support memory devices such as NAND flash and

asynchronous SRAM, peripheral devices such as LCDs, and the UBM receiver for multicast or

broadcast reception (QSC6270 only). In addition, EBI2 is required to support a synchronous-burst

AAD NOR flash to enable a NOR/DDR SDRAM memory configuration because the simultaneous mode

(NOR, SDRAM) is not supported on the EBI1 bus.

The ARM926EJ-S microprocessor is a cached processor and all its accesses to external memory use burst

techniques of four or eight 32-bit words when the memory region is declared to be

cacheable/bufferable. To take advantage of this QSC higher performance feature, data from

memories must satisfy the requirements for these burst accesses.

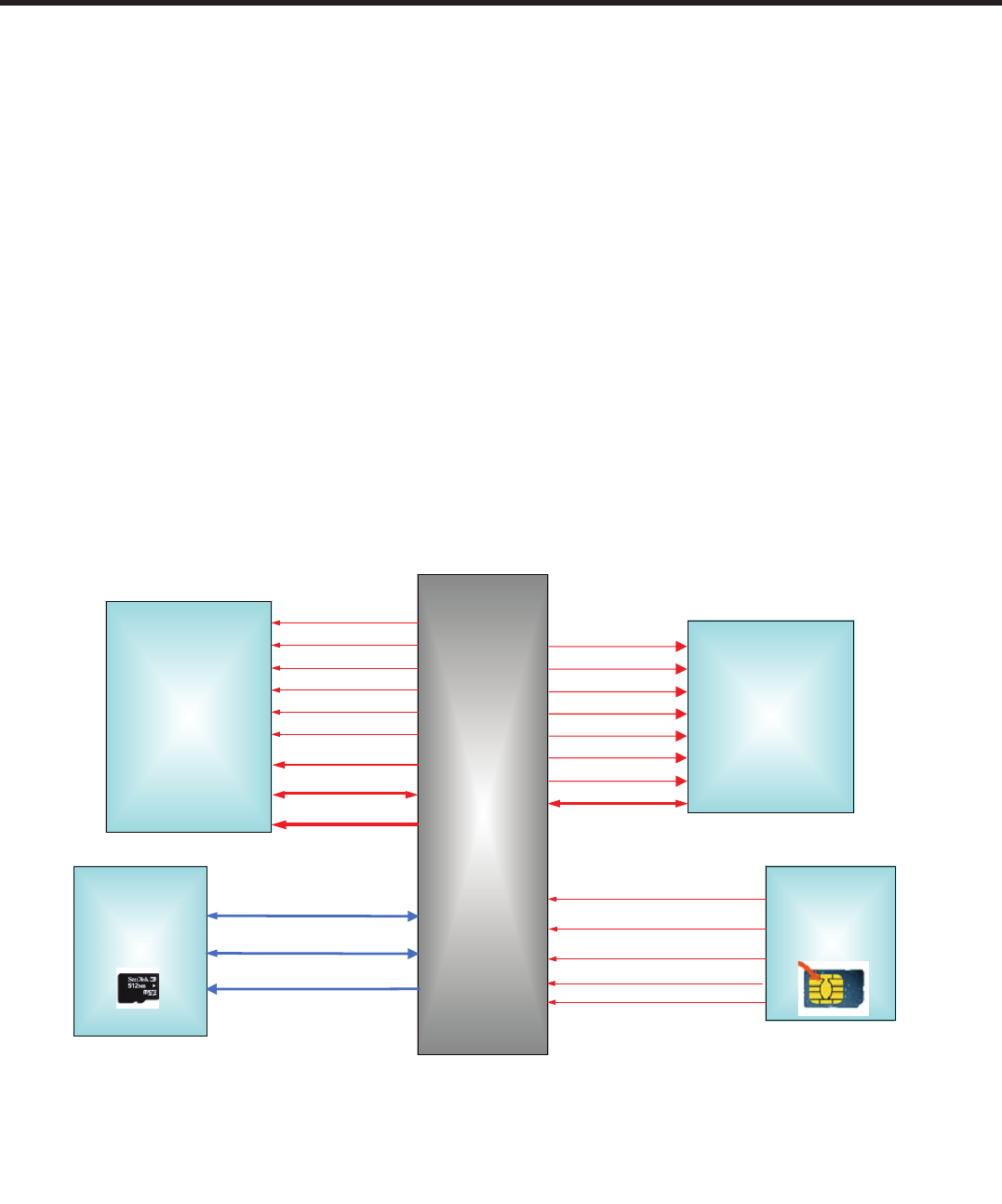

Figure 3.1.2.1 The memory control blocks of C320

QSC6270

NAND Flash

(1Gbit)

SDRAM

512Mbit)

NAND_DATA[0: 15]

NAND__CS__N

NAND_LB_N

NAND_UB_N

NAND_OE_N

NAND_WE_N

NAND_BSY_N

NAND_WP_N

_CE

ALE

CLE

_RE

_WE

RY_BY

_WP

IO[1: 16]

DDR_A[0:13]

DDR_M_CLK_N

DDR_CKE[0]_

DDR_CS[0]_N_

DDR_RAS_N

DDR_CAS_N

DDR_WE_N_ _

DDR_DQM[0:1]_

DDR_D[0:15]

CLK

CKE

_CS

_RAS

_CAS

_WED

DQM

ADDR

DQ

EBI1

EBI2

(3G disable)

USIM

(SIM PLUS)

SIM_CLK

_ _

SIM_DATA

MUSIM_DM

MUSIM_DP

SIM_RST_N

External

Memory

( MICRO SD)

MSD_D[0:3]

MSD_CMD

MSD_CLK

3.1.2 Memory support (and LCD interface)

The QSC62x0 device has two external bus interface (EBI) ports: EBI1 and EBI2.

EBI1 supports high-speed synchronous dynamic devices. Its memory controller supports the new mobile DDR

SDRAM memories with its higher bandwidth and ability to run at high clock frequencies. This interface supports

the high-bandwidth, high-density, and low-latency requirements of the QSC’s advanced on-chip capabilities such

as the ARM9 processor, highperformance graphics, and video applications.

EBI2 is the slower speed interface intended to support memory devices such as NAND flash and asynchronous

SRAM, peripheral devices such as LCDs, and the UBM receiver for multicast or broadcast reception (QSC6270 only).

In addition, EBI2 is required to support a synchronous-burst AAD NOR flash to enable a NOR/DDR SDRAM memory

configuration because the simultaneous mode (NOR, SDRAM) is not supported on the EBI1 bus.

The ARM926EJ-S microprocessor is a cached processor and all its accesses to external memory use burst

techniques of four or eight 32-bit words when the memory region is declared to be cacheable/bufferable. To take

advantage of this QSC higher performance feature, data from memories must satisfy the requirements for these

burst accesses.