Chapter 1 Overview

8

1-3-2 Pin Function Summary

*The pin numbers in the list correspond to the QFH package(Refer

to Figure 1-3-3 Pin connection.) Be careful when using SDIP and

QFP packages.

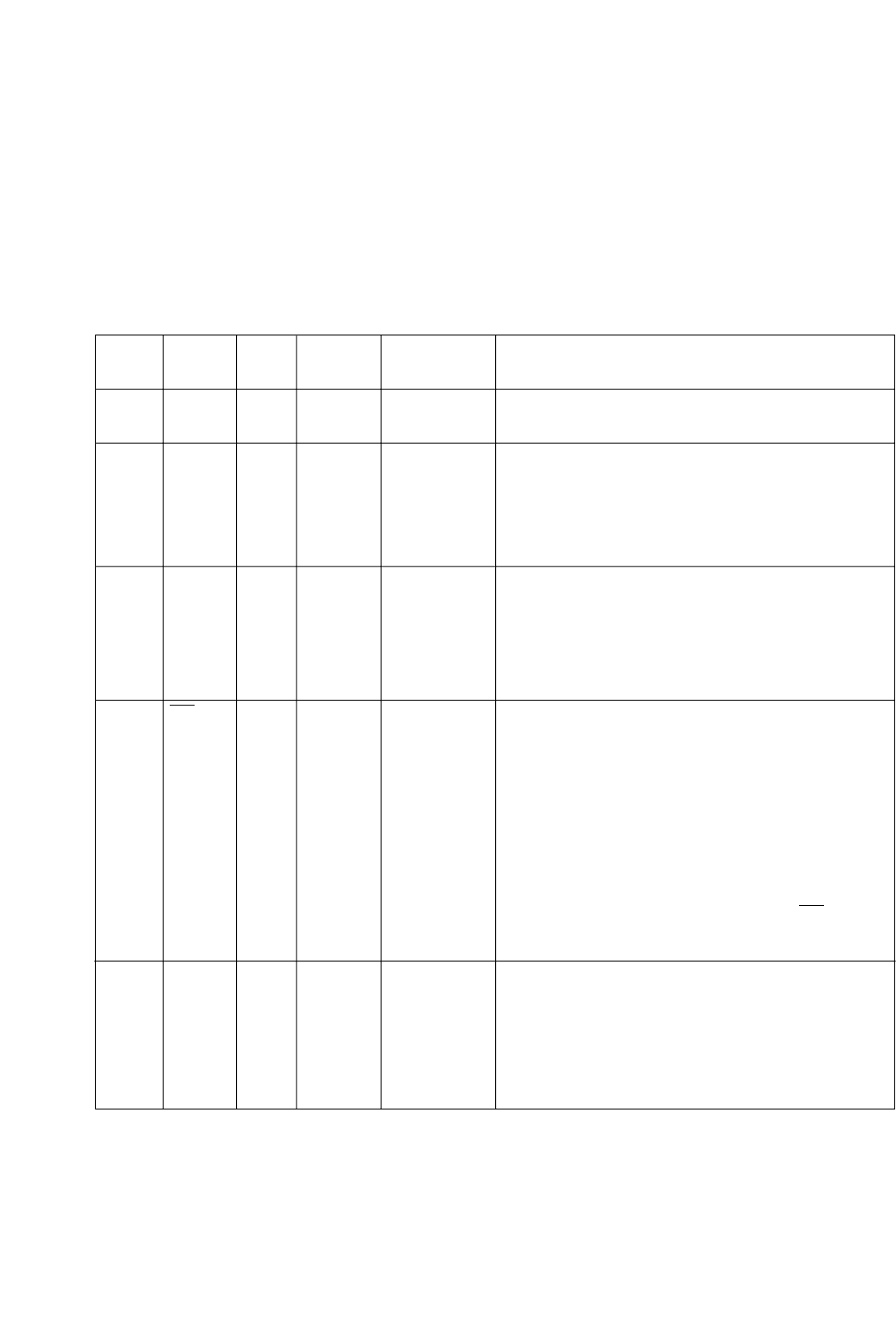

Table 1-3-1 Pin Function Summary (1/4)

Pins

Pin No. Name Type Dual Function Function Description

17 VSS – Power supply pins Apply 2.0V to 5.5V to VDD and 0V to VSS.

14 VDD

16 OSC1 Input Clock input pin

Connect these oscillation pins to ceramic or crystal oscillators for high-

15 OSC2 Output Clock output pin

speed clock operation.

If the clock is an external input, connect it to OSC1 and leave OSC2

open. The chip will not operate with an external clock when using either

the STOP or SLOW modes.

18 XI Input Clock input pin

Connect these oscillation pins to ceramic or crystal oscillators for low-

19 XO Output Clock output pin

speed clock operation.

If the clock is an external input, connect it to XI and leave XO open.

The chip will not operate with an external clock when using the STOP

mode. If these pins are not used, connect XI to VSS and leave XO open.

*42-SDIP and 44-QFP packages have no pins of this kind.

43 RST I/O P27 Reset pin This pin resets the chip when power is turned on, is allocated as P27 and

contains an internal pull-up resistor (Typ. 35 kΩ).

Setting this pin low initializes, the internal state of the device

is initialized. Thereafter, setting the input to an"H"level release the reset

The hardware waits for the system clock to stabilize, and then

processes the reset interrupt.

Also, if "0" is written to P27 and the reset is initiated by software, a low

level will be output. The output has an n-channel open-drain configuration.

If a capacitor is to be inserted between RST and VDD, it is

recommended that a discharge diode be placed between RST and VDD.

20 to 23 P00 to P02 I/O SBO0(TXD), I/O port 0 4-bit CMOS tri-state I/O port.

P06 SBI0(RXD), Each bit can be set individually as either an input or output by the

SBT0, P0DIR register. A pull-up resistor for each bit can be selected

DK individually by the P0PLU register.

(BUZZER) At reset, the input mode is selected and pull-up resistors are disabled

(high impedance output).