Chapter 2 Basic CPU Functions

36

Reset

2-5 Reset

The CPU contents are reset and registers are initialized when the RST pin is

pulled to low.

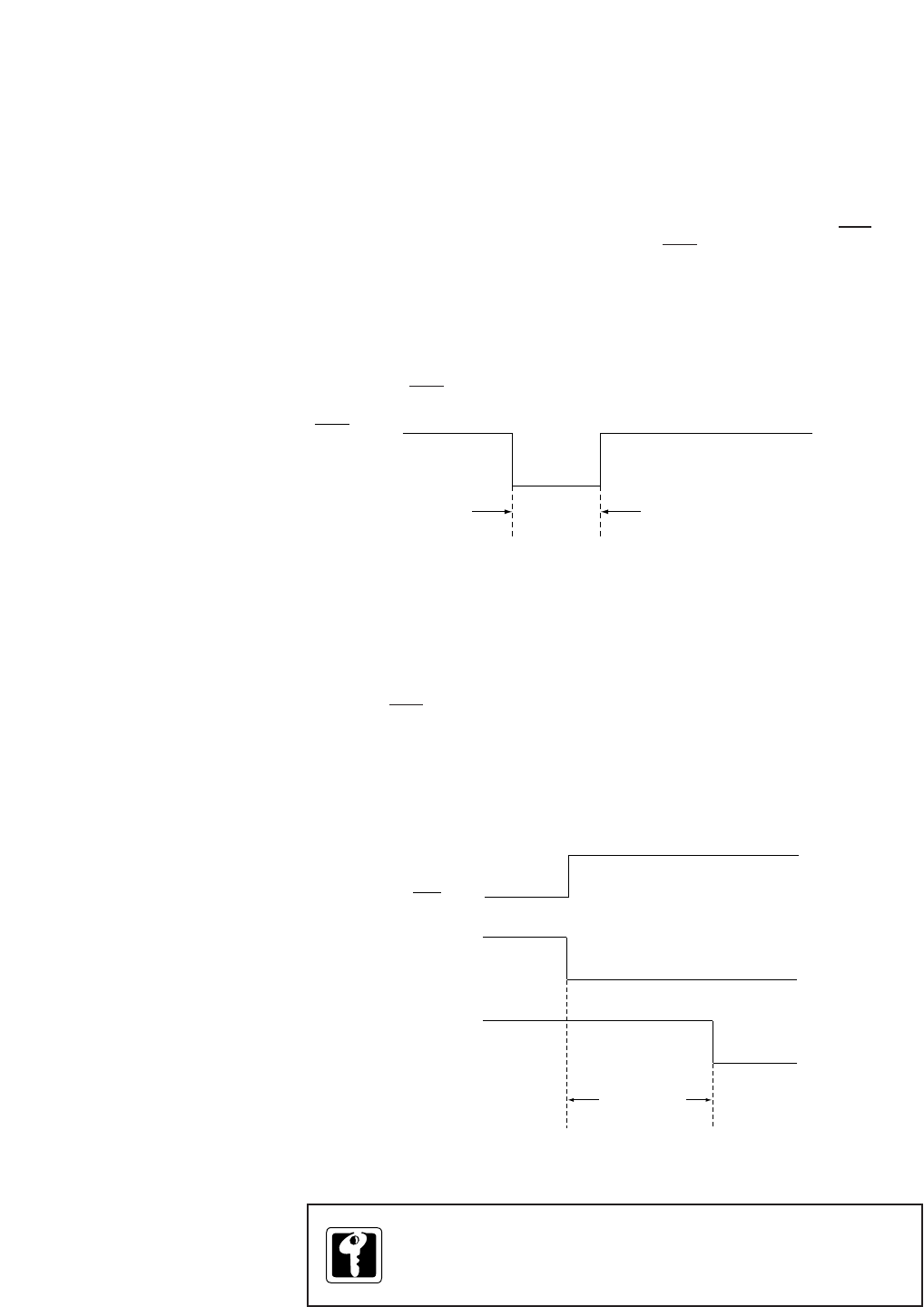

■ Initiating a Reset

There are two methods to initiate a reset.

(1) Drive the RST pin low for at least four clock cycles.

Figure 2-5-1 Minimum Reset Pulse Width

(2) Set bit 7 (P2OUT7 flags) of the P2OUT register to "0." After reset is released,

the P2OUT flag will be "1."

■ Releasing the Reset

When the RST pin changes from low to high, an internal 15-bit counter begins

counting at the oscillation clock frequency. The interval from when this counter

begins counting until it overflows is known as the stabilization wait time. After

waiting for this amount of time, the internal reset is released and the CPU begins

operation.

Figure 2-5-2 Reset Release Sequence

RST pin

4 clock cycles

(200ns for a 20MHz oscillation)

For the reset to be stable, the

low pulse must be maintained

for at least four clock cycles.

However, it is important to

minimize noise, since a reset

may occur in a smaller number

of clock cycles.

Oscillation

stabilization wait time

2 /fosc

RST pin

Peripheral

register

CPU

internal reset

15

When returning from the STOP mode is terminating, the

software can use the DLYCTR register to select an

oscillation stabilization wait time of 0, 2

7

/fosc, 2

11

/fosc, or

2

15

/fosc.