Chapter 4 Timer Functions

66

If the TM3PWM flag of the TM3MD

register is set to "1" and timer 2

PWM output is selected, the PWM

output of timer 2 will also be output

from the TM3IO pin.

If port 1 is to be used as a PWM

output pin, the P1DIR and P1PLU

registers must be set.

■ PWM Output Function (Timer 2)

Settings for the PWM output function are listed below.

(1) Set the TM2EN flag of the timer 2 mode register (TM2MD) to "0" to stop the count

operation of timer 2.

(2) Set bit 2 of the port 1 output/input mode register (P1OMD) to the special function

pin setting. Bit 2 of port 1 will be specified as the PWM output pin.

(3) Set the TM2CK2 to 0 flags of the TM2MD register to select fs, fs/4, fx, or

synchronous fx as the clock source. The period of the output waveform is determined

based on the clock source.

(4) Set the TM2PWM flag of the TM2MD register to "1" so that PWM operation is

selected.

(5) Set a value in compare register 2 (TM2OC). The high interval of the output

waveform is determined based on the value of the TM2OC compare register.

(6) Set the TM2EN flag of the TM2MD register to "1" to start the timer.

(7) When timer 2 begins operation, binary counter 2 will count upward from X'00'.

(8) A high-level signal is output from the port beginning when binary counter 2 starts

counting at X'00' and ending when the value of binary counter 2 matches the value

set in the TM2OC register.

(9) When the value of binary counter 2 matches that of the TM2OC register, a low-level

signal is output from the port.

(10) Binary counter 2 continues to count upward until X'FF' is reached. At the next count-

up cycle, the value of binary counter 2 is reset to X'00', a high-level signal is output

from the port, and counting begins again.

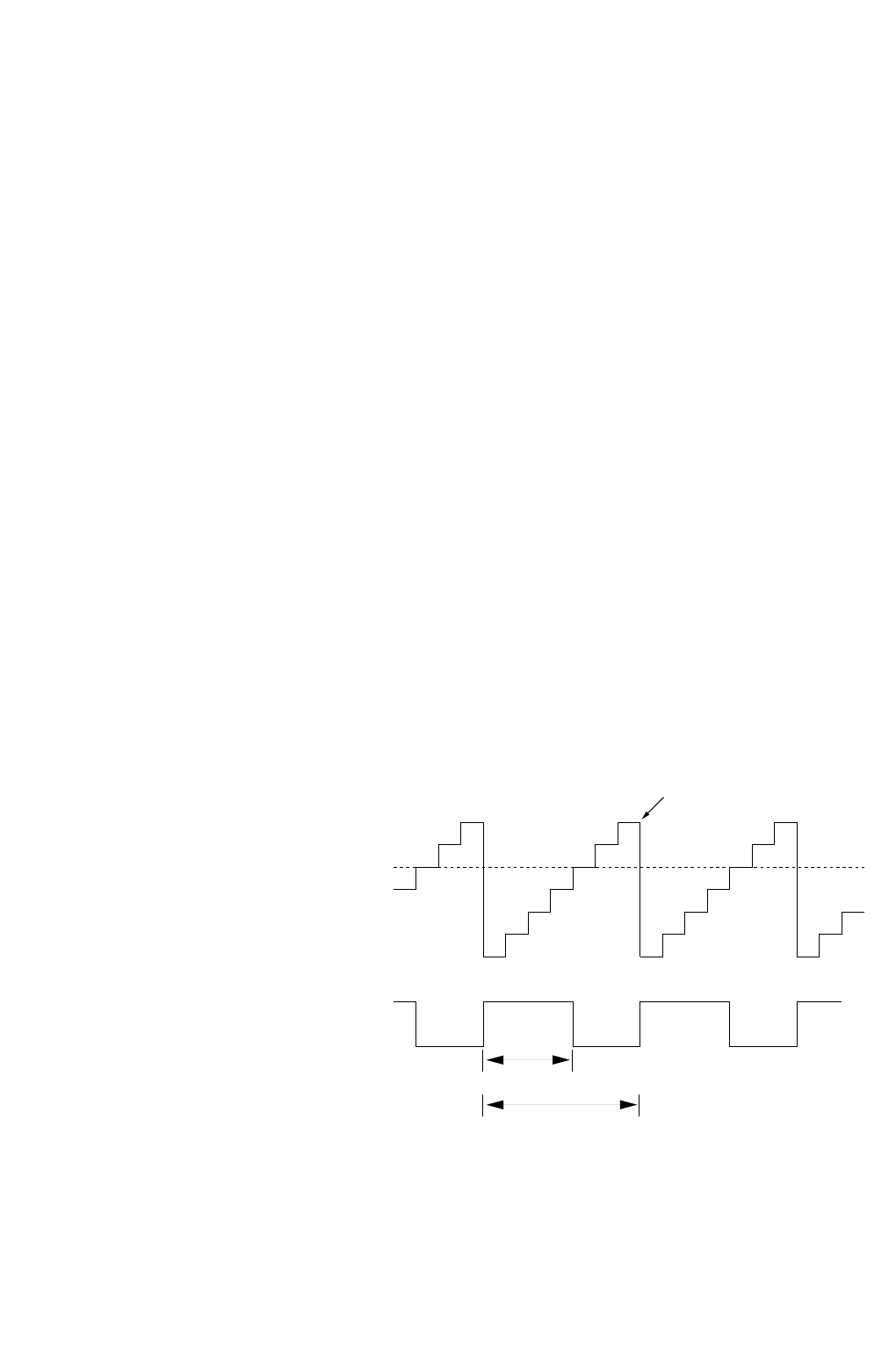

Figure 4-2-4 PWM Output Timing

Binary

counter 2

Overflow

Matches TM2OC

register

PWM output

Time specified by TM2OC register

Time until binary counter 2 reaches X'FF'

8-bit Timer Operation (timers 2, 3)