2-3 Bus Interface

2-3-1 Overview

The MN101C117, unlike other MN101C series microcomputers, does not

support memory expansion mode and processor mode.

2-3-2 Control Registers

The memory control register is a four-bit register that sets up wait-count at a

time of access to a base address of interrupt vector table and a special

register zone.

(1) Memory control register(MEMCTR)

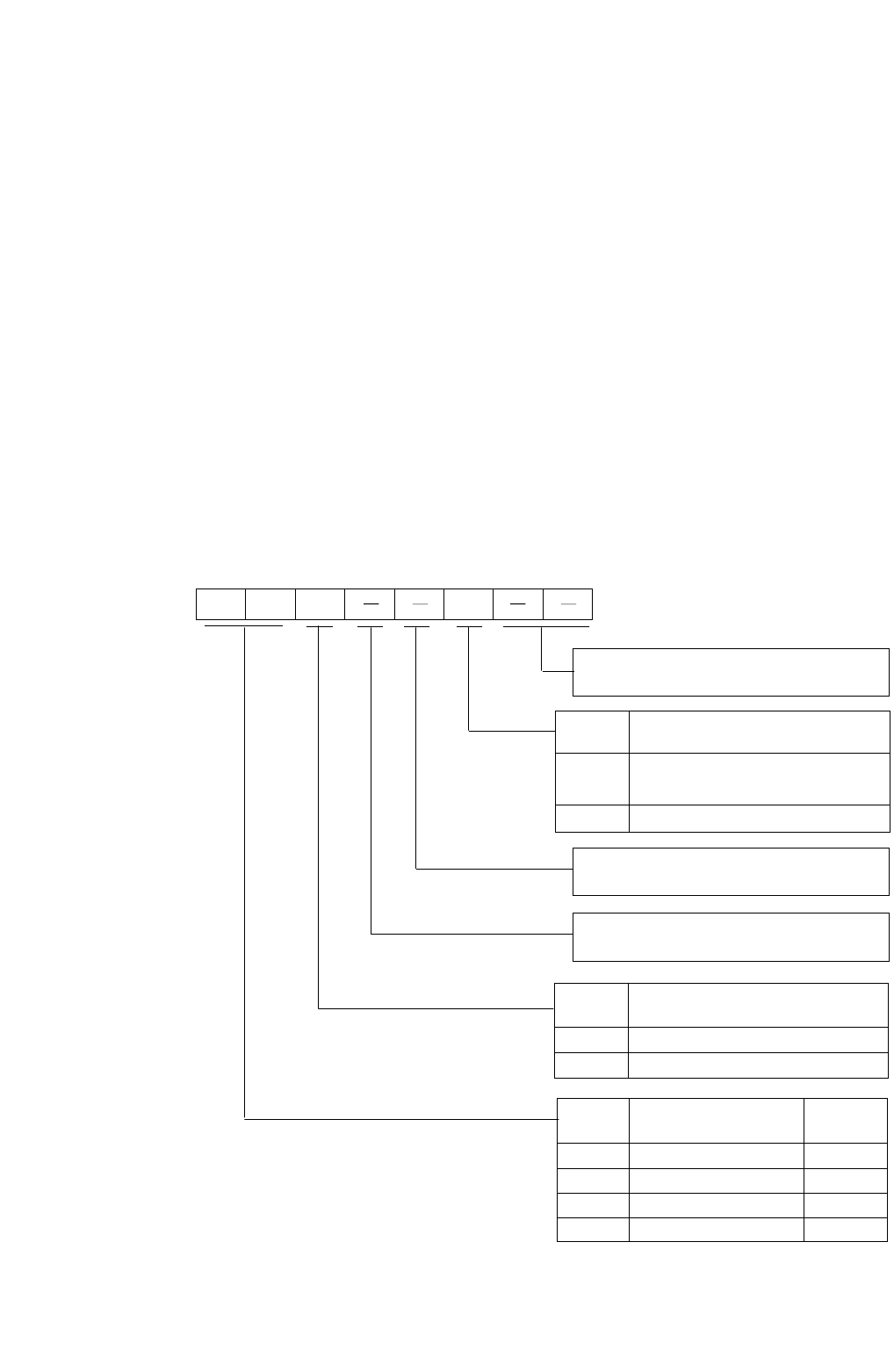

Figure 2-3-1 Memory Control Register MEMCTR:X'03F01'R/W

Chapter 2 Basic CPU Functions

30

Bus Interface

76543210

MEMCTR

IOW1

IOW0

IRWE

IRWE

Set software write for interrupt request flag

0

1

Software write disable

Even if data is written to each interrupt control

register (xxxICR), the state of the interrupt

request flag (xxxIR) will not change.

Software write enable

IOW1 to 0

Number of wait cycles set when

accessing special register area

00

01

10

11

No wait cycles

1 wait cycle

2 wait cycles

3 wait cycles

Bus cycle at

20MHz oscillation

100ns

150ns

200ns

250ns

IVBA

IVBA

Base address setting for interrupt vector table

0

Interrupt vector base = X'04000'

Interrupt vector base = X'00100'

1

(at reset: 11001011)

Must be set to 11.

Must be set to 1.

Must be set to 0