2-4-3 Interrupt Control Registers

Interrupt control registers consist of the following: a non-maskable interrupt control

register (NMICR), external interrupt control registers (IRQnICR), and internal

interrupt control registers (TMnICR, TBICR, SCnICR, ATCICR, ADICR).

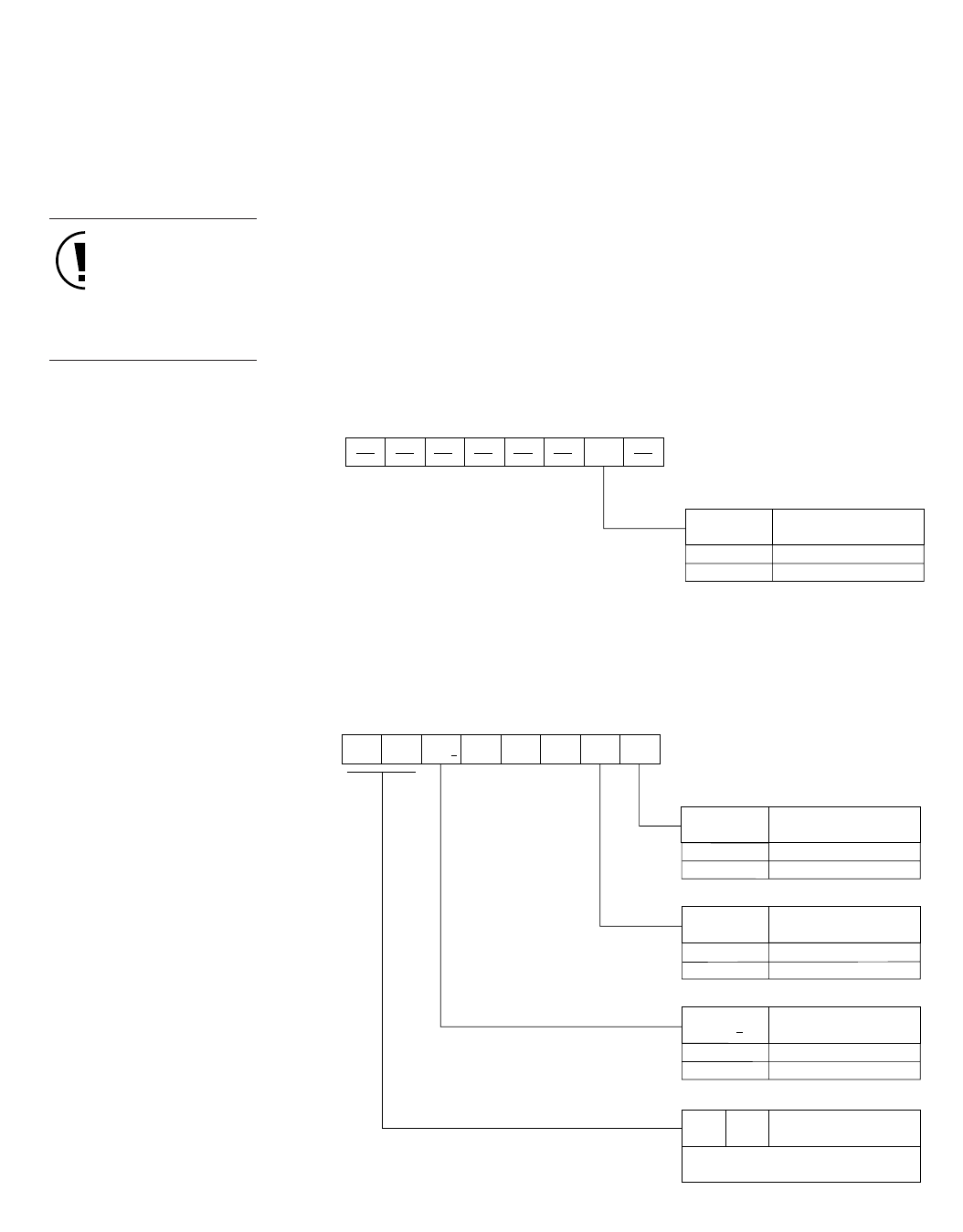

■ Non-maskable Interrupt Control Register (NMICR)

Non-maskable interrupt factors are stored in the non-maskable interrupt control

register (NMICR), and are used when a non-maskable interrupt is generated.

Figure 2-4-2 Non-maskable Interrupt Control Register (NMICR: X'03FE1', R/W)

■ External Interrupt Control Registers (IRQnICR)

The external interrupt control registers (IRQnICR) control the interrupt level, valid

edge, and request/enable.

Figure 2-4-3 External Interrupt Control Register

(IRQnICR: X'03FE2' to X'03FE3', X'03FEB' to X'03FED', R/W)

Chapter 2 Basic CPU Functions

34

Interrupts

01245673

(at reset: ------0-)

NMICR

0

1

No interrupt request

Watchdog interrupt request flag

Happens interrupt request

WDIR

WDIR

xxxLV1

Interrupt level flag for external interrupt

xxxLV0

01245673

(at reset: 000---00)

IRQnICR

0

1

No interrupt request

External interrupt request flag

Happens interrupt request

xxxIE

xxxIR

0

1

Disable interrupt

External interrupt enable flag

Enable interrupt

xxxIE

0

1 Rising edge

External interrupt valid edge flag

Falling edge

The CPU has interrupt levels from 0 to 3.

This flag sets the interrupt level for interrupt requests.

REDGn

∗

xxxIRxxxLV1xxxLV0

REDGn

———

∗ n=0,1,2,3,4

By setting xxxLVn to '11' (level

3), the corresponding interrupt

vector will be disabled,

regardless of the state of the

interrupt enable and interrupt

request flags.

Be sure to use the MIE flag of

the PSW register to write to all

interrupt control registers.