NDA-24300 CHAPTER 5

Page 357

Issue 1

FAULT REPAIR PROCEDURES

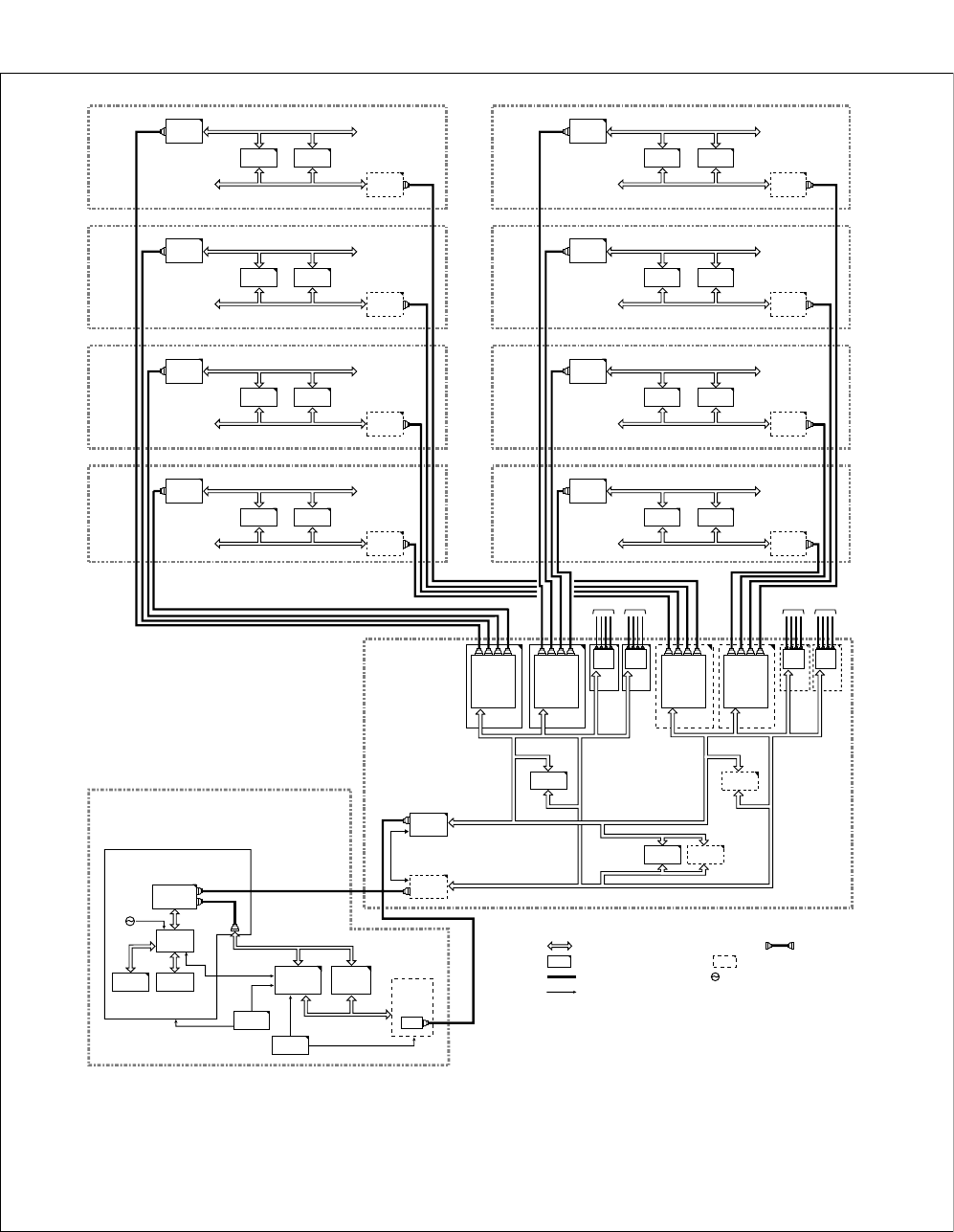

Figure 5-9 CPU Controlling Block Diagram

LPM

EMA

IOC /

MISC

ISAGT 0

LANI

PWR

PWR

CPU 0

MEMORY

PCI BUS

ISA BUS

CPU board

CPR

CPU clock

CPR

(ST-BY)

Reset Signal

MISC BUS

MISC BUS

ISAGT 1

T

M

T

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

IMG0

PIM 3

PIM 2

PIM 1

PIM 0

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

LC/TRK

MUX

MUX

LC/TRK

PM BUS

PM BUS

IMG1

PIM 3

PIM 2

PIM 1

PIM 0

Note 1: The circuit cards, drawn by dotted lines, indicate they are in STBY state. These cards (TSW, MUX and

DLKC) are totally changed over to the ACT mode, when the MBR key of the active GT (PH-GT09) card is

once flipped. However, PLO (PH-CK16/17/16-A/17-A) is independent and not affected by the development.

Symbols

: Controlling Routes of CPU : Cable

: Circuit card (active) : Circuit card (STBY)

: External Cable : Clock Oscillator

: Signral

EMA: PH-PC40 ISAGT: PZ-GT13

LANI: PZ-PC19 GT: PH-GT09

IOC: PH-IO24 TSW: PH-SW12

DLKC: PH-PC20 PLO: PH-CK16/17/16-A/17-A

MUX: PH-PC36

TSWM

TSW 00 TSW 10 TSW 11TSW 01

PLO 0 PLO 1

DLKC 1

DLKC 0

DLKC 1

GT 1

GT 0

MISC BUS

MISC BUS

MISC BUS

MISC BUS

MISC BUS

MISC BUS

TSW

02

TSW

03

TSW

13

TSW

12

To IMG 2To IMG 3 To IMG 3To IMG 2

IOP1

IOP0

TSW/INT TSW/INT TSW/INTTSW/INT

M

U

X

003

M

U

X

002

M

U

X

001

M

U

X

000

M

U

X

013

M

U

X

012

M

U

X

011

M

U

X

010

M

U

X

100

M

U

X

101

M

U

X

102

M

U

X

103

M

U

X

110

M

U

X

111

M

U

X

112

M

U

X

113

TSW

/INT

TSW

/INT

TSW

/INT

TSW

/INT

Note 1

Note 3

Note 2

Note 2: If the ACT/STBY of CPU is once changed over, the system of GT (in TSWM) also changes over.

Note 3: Though an external cable is physically connected between ISAGT0 and GT1, the actual control signal is

sent/received only between ISAGT0 and GT0. This is because GT0 and GT1 are having a multiple connection

on the backboard side. (Refer to Chapter 6, Section 12.)

BUS

TSW I/O

BUS

TSW I/O