VI - 19

Chapter 6 8-bit Timers

8-bit Event Count

M

N

00 01 02 N-1

N

00 01

TMnIO

input

TMnEN

flag

Compare

register

Binary

counter

Interrupt

request flag

6-4 8-bit Event Count

6-4-1 Operation

Event count operation has 2 types ; TMnIO input and synchronous TMnIO input can be selected as the

count clock.

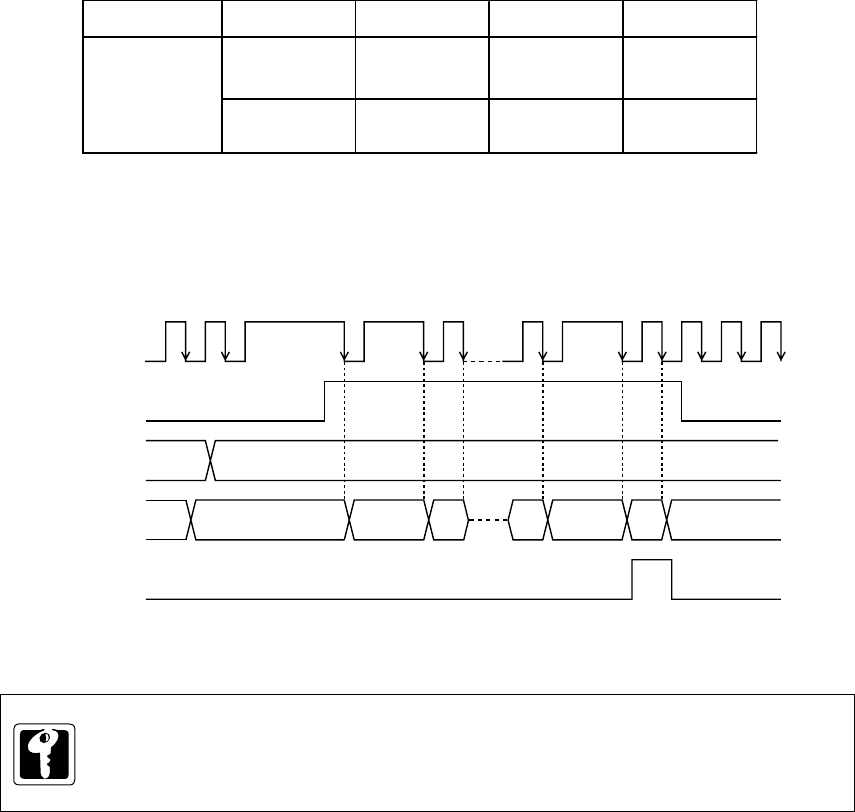

8-bit Event Count Operation

Event count means that the binary counter (TMnBC) counts the input signal from external to the TMnIO

pin. If the value of the binary counter reaches the setting value of the compare register (TMnOC), inter-

rupts can be generated at the next count clock.

Count Timing of TMnIO Input (Timers 0, 1, 4 and 5)

When TMnIO input is selected, TMnIO input signal is directly input to the count clock of the timer n. The

binary counter counts up at the falling edge of the TMnIO input signal.

Table 6-4-1 Event Count Input Clock

Figure 6-4-1 Count Timing of TMnIO Input (Timers 0, 1, 4 and 5)

When the TMnIO input is selected for count clock source and the value of the timer n binary

counter is read during operation, incorrect value at count up may be read out. To prevent

this, use the event count by synchronous TMnIO input, as the following page.

Timer 0Timer 2Timer 4Timer 5

TM0IO input TM1IO input TM4IO input TM5IO input

(P11) (P76) (P13) (P77)

Synchronous

TM0IO input

Synchronous

TM1IO input

Synchronous

TM4IO input

Synchronous

TM5IO input

Event Input