Chapter 7 16-bit Timer

VII - 24

16-bit Standard PWM Output

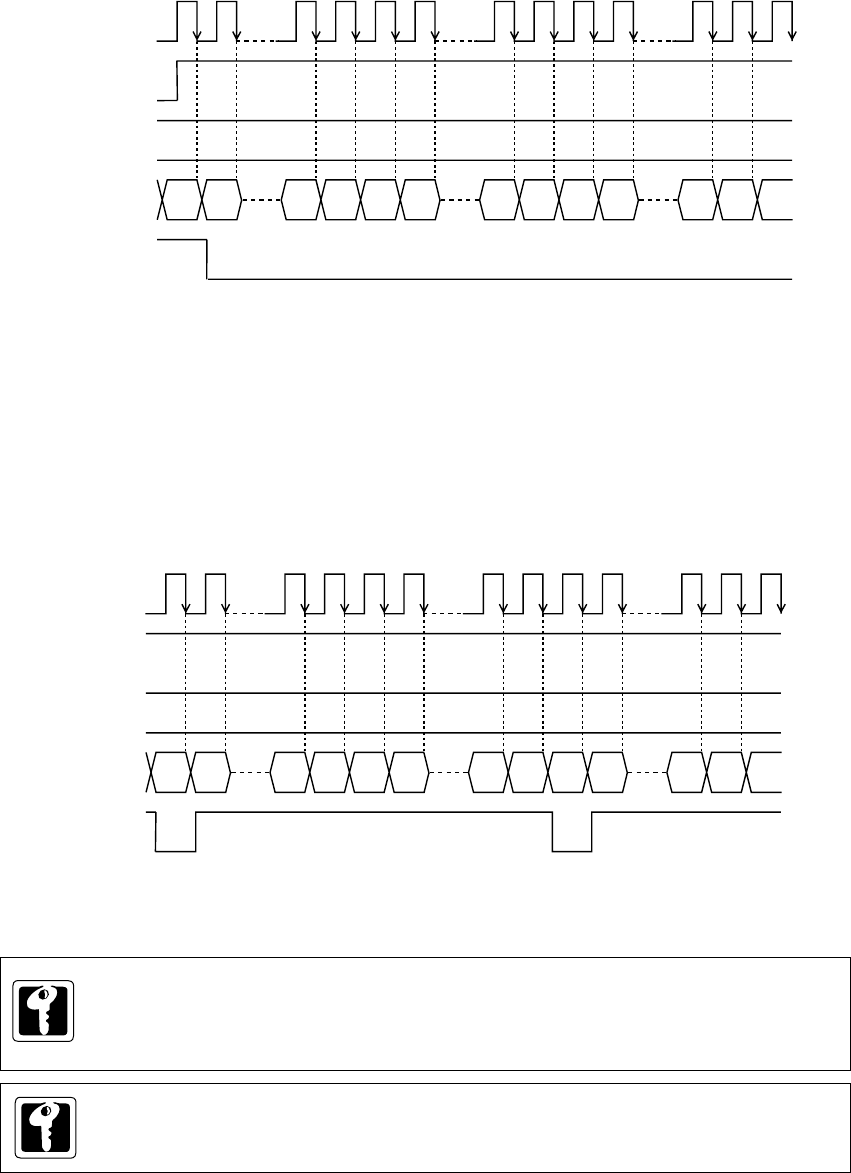

Count Timing of Standard PWM Output (when Compare Register 1 is x'0000')(Timer 7)

Here is the count timing at setting x'0000' to the compare register 1.

Figure 7-6-3 Count Timing of Standard PWM Output (when Compare Register 1 is x'FFFF')

Figure 7-6-2 Count Timing of Standard PWM Output (when Compare Register 1 is x'0000')

Count Timing of Standard PWM Output (when Compare Register 1 is x'FFFF')(Timer 7)

Here is the count timing at setting x'FFFF' to the compare register 1.

PWM output shows "H ", when TM7EN flag is stopped (at "0").

When the standard PWM output is operated, set the TM7BCR flag of the TM7MD2 register to

"0" to select the full count over flow as a binary counter clear source and a PWM output setup

("H" output) source.

0000

N+1 N+2 FFFE

FFFF

Count

clock

TM7EN

flag

Compare

regsiter 1

Binary

counter

0000 0001 N+1N-1

N

0000 0001 N-1

N

TM7IO output

(PWM output)

H

L

FFFF

N+1 N+2 FFFE

FFFF

Count

clock

TM7EN

flag

Compare

register 1

Binary

counter

0000 0001 N+1N-1

N

0000 0001 N-1

N

TM7IO output

(PWM output)

By setting the T7PWMSL flag of the TM7MD2 register, the TM7OC1 compare match or the

TM7OC2 compare match can be selected as a PWM output reset ("L" output) source.