Chapter 11 Serial Interface 0, 1

XI - 4

Overview

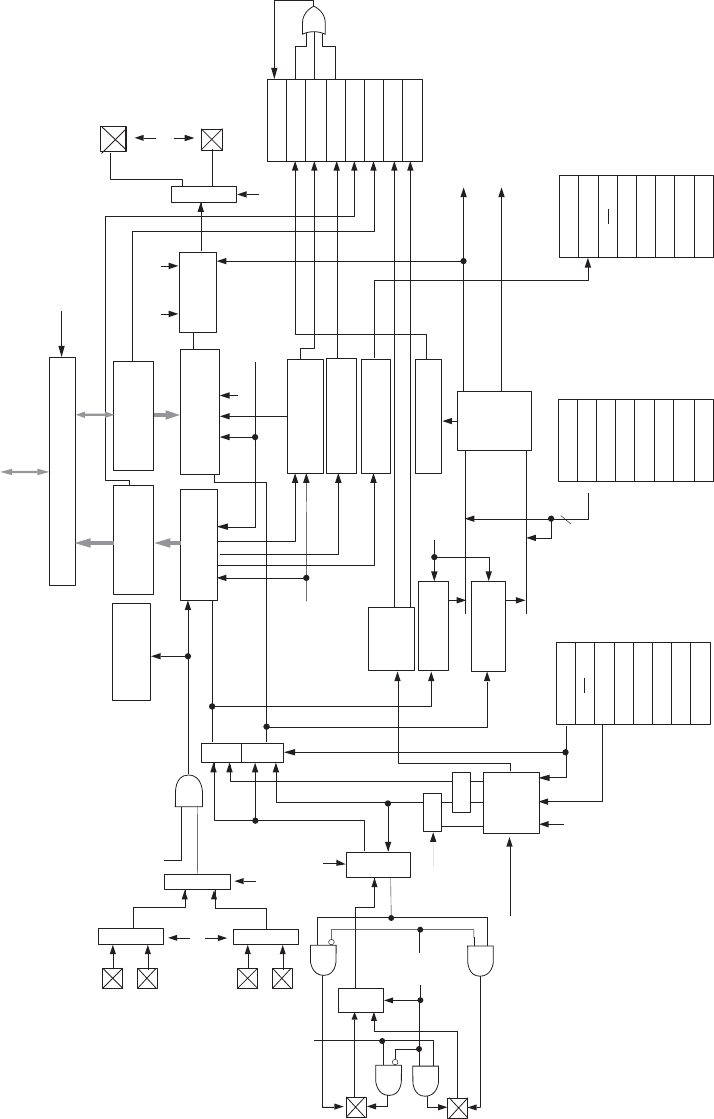

11-1-2 Block Diagram

Serial Interface 0 Block Diagram

Figure 11-1-1 Serial Interface 0 Block Diagram

Reception shift register

SBO0B/P70

SC0RIRQ

Start condition

generation circuit

3

IRQ

control

circuit

Clocl

control

circuit

match

Reception bit

counter

BUSY

generation

circuit

Received buffer

Transmission shift register

Parity bit control

circuit

Start condition

detection circuit

MUX

M

U

X

M

U

X

match

break status

received monitor

Transmission buffer

SC0MD3

SC0MD2

SC0MD1

SC0MD0

Transmission

bit counter

SC0TIRQ

0

7

SC0ERE

SC0ORE

SC0PEK

SC0FEF

SC0RBSY

SC0TBSY

SC0REMP

SC0TEMP

SC0IOM

SC0CMD

SC0SBIS

SC0SBOS

SC0SBTS

SC0CKM

0

7

SC0MST

SC0BRKF

SC0BRKE

SC0NPE

SC0PM0

SC0PM1

SC0FM0

SC0FM1

0

7

1/8

sc0psc

(prescaler output)

SC0CE1

SC0STE

SC0DIR

SC0LNG0

SC0LNG1

SC0LNG2

0

7

SC0CKM

SC0DIR

SC0STESC0CMD

SC0STE

Stop bit detection

circuit

Overrun error detection

SC0FM0

SC0FM1

SC0NPE

SC0FM0

SC0FM1

SC0PM0

SC0PM1

SCOSBOS

SC0SBIS

SC0BRKE

Read/Write

SC0RDB

SC0TRB

RXBUF0

TXBUF0

SWAP MSB<->LSB

SC0REN

SC0TRN

M

U

X

M

U

X

M

U

X

SB0IOM

SC0SEL

SBI0A/P04

SBI

0B/P71

SBO0A/P03

SBO0B/P70

P

O

L

SC0CE1

SBT0A/P05

M

U

X

SCOSEL

SBT0B/P72

SCOSBTS

SBO0A/P03

M

U

X

SCOSEL

}

}

}