Chapter 17 Appendices

XVII - 10

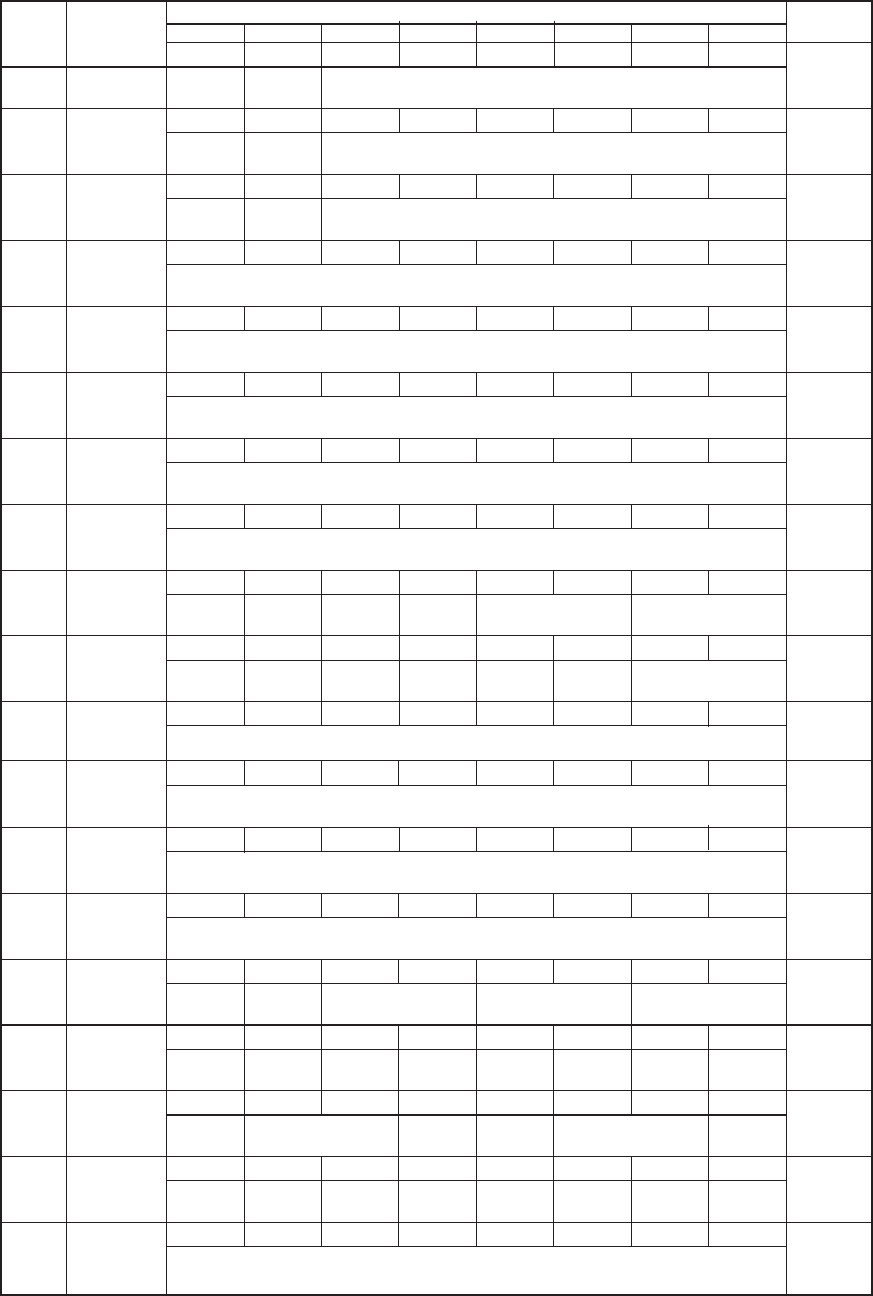

Special Function Registers List

Timer 7 Count Clock

Selection

Timer 7 Clock Source

Selection

Timer 7 Capture Trigger

Selection

X'3F70'

X'3F71'

X'3F72'

Address

X'3F73'

X'3F74'

X'3F75'

X'3F76'

X'3F77'

X'3F78'

X'3F79'

X'3F7A'

Bit 7

TM7BCL7

TM7BCH7

TM7OC1L7

TM7OC1H7

TM7PR1L7

TM7PR1H7

TM7ICL7

TM7ICH7

Reserved

Set Always

to "0"

T7ICEDG

Capture Trigger

Edge Selection

TM7OC2L7

Bit 6

TM7BCL6

TM7BCH6

TM7OC1L6

TM7OC1H6

TM7PR1L6

TM7PR1H6

TM7ICL6

TM7ICH6

Reserved

Set Always

to "0"

T7PWMSL

PWM Mode

Selection

TM7OC2L6

Bit 5

TM7BCL5

TM7BCH5

TM7OC1L5

TM7OC1H5

TM7PR1L5

TM7PR1H5

TM7ICL5

TM7ICH5

TM7CL

Timer 7

Output Reset

Control

TM7BCR

Clear Factor

Selection

TM7OC2L5

Bit 4

TM7BCL4

TM7BCH4

TM7OC1L4

TM7OC1H4

TM7PR1L4

TM7PR1H4

TM7ICL4

TM7ICH4

TM7EN

Timer 7

Count Control

TM7PWM

Timer 7 Output

Selection

TM7OC2L4

Bit 3

TM7BCL3

TM7BCH3

TM7OC1L3

TM7OC1H3

TM7PR1L3

TM7PR1H3

TM7ICL3

TM7ICH3

TM7PS1

TM7IRS1

Timer 7 Interrupt

Factor Selection

TM7OC2L3

Bit 2

TM7BCL2

TM7BCH2

TM7OC1L2

TM7OC1H2

TM7PR1L2

TM7PR1H2

TM7ICL2

TM7ICH2

TM7PS0

T7ICEN

Enable Capture

Operation

TM7OC2L2

Bit 1

TM7BCL1

TM7BCH1

TM7OC1L1

TM7OC1H1

TM7PR1L1

TM7PR1H1

TM7ICL1

TM7ICH1

TM7CK1

T7ICT1

TM7OC2L1

Bit 7

TM7BCL0

TM7BCH0

TM7OC1L0

TM7OC1H0

TM7PR1L0

TM7PR1H0

TM7ICL0

TM7ICH0

TM7CK0

T7ICT0

TM7OC2L0

Register

TM7BCL

TM7BCH

TM7OC1L

TM7OC1H

TM7PR1L

TM7PR1H

TM7ICL

TM7ICH

TM7MD1

TM7MD2

TM7OC2L

Bit Symbol /Initial Value /Description

Timer 7 Binary Counter Lower 8 Bits

Timer 7 Binary Counter Upper 8 Bits

Timer 7 Output Compare Register 1 Lower 8 Bits

Timer 7 Output Compare Register 1 Upper 8 Bits

Timer 7 Preset Register 1 Lower 8 Bits

Timer 7 Preset Register 1 Upper 8 Bits

Timer 7 Input Capture Register Lower 8 Bits

Timer 7 Input Capture Register Upper 8 Bits

Timer 7 Output Compare Register 2 Lower 8 Bits

Page

VII - 7

VII - 7

VII - 5

VII - 5

VII - 6

VII - 6

VII - 7

VII - 7

VII - 8

VII - 9

VII - 5

X'3F7C'

X'3F7D'

X'3F7E'

X'3F8D'

X'3F8F'

TM7PR2L7 TM7PR2L6 TM7PR2L5 TM7PR2L4 TM7PR2L3 TM7PR2L2 TM7PR2L1 TM7PR2L0

TM7PR2L Timer 7 Preset Register 2 Lower 8 Bits VII - 6

TM7PR2H7 TM7PR2H6 TM7PR2H5 TM7PR2H4 TM7PR2H3 TM7PR2H2 TM7PR2H1 TM7PR2H0

TM7PR2H

Timer 7 Preset Register 2 Upper 8 Bits

VII - 6

- - P1CNT5 P1CNT4 P1CNT3 P1CNT2 P1CNT1 P1CNT0

P1TCNT P12 Output Data Control P10 Output Data Control IV - 15

P14 Output Data Control

- - - - NF4EN NF3EN NF2EN

NFCTR1 IRQ2 Noise

Filter Enable

IRQ3 Noise

Filter Enable

IRQ4 Noise

Filter Enable

III - 44

III - 43

- - Reserved EDGSEL4 EDGSEL3 EDGSEL2 EDGSEL1 EDGSEL0

EDGDT

IRQ3 Both Edge

Specification

IRQ2 Both Edge

Specification

IRQ1 Both Edge

Specification

IRQ0 Both Edge

Specification

Set Always

to "0"

IRQ4 Both Edge

Specification

III - 45

X'3F8E'

P21IM NF1SCK1 NF1SCK0 NF1EN - NF0SCK1 NF0SCK0 NF0EN

NFCTR0

ACZ Input

Enable Flag

IRQ1 Noise Filter

Sampling Period Selection

IRQ1 Noise

Filter Enable

IRQ0 Noise Filter

Sampling Period Selection

IRQ0 Noise

Filter Enable

X'3F90'

RXBUF07 RXBUF06 RXBUF05 RXBUF04

RXBUF03

RXBUF02 RXBUF01 RXBUF00

RXBUF0

Serial Interface 0 Data Reception Buffer

XI - 7

X'3F7B'

TM7OC2H7 TM7OC2H6 TM7OC2H5 TM7OC2H4 TM7OC2H3 TM7OC2H2 TM7OC2H1 TM7OC2H0

TM7OC2H

Timer 7 Output Compare Register 2 Upper 8 Bits

VII - 5

-