XI - 27

Chapter 11 Serial Interface 0, 1

Operation

Emergency Reset

It is possible to shut down communication. For a forced reset, the SCnSBOS flag and the SCnSBIOS

flag of the SCnMD1 register should be set to "0" (SBO pin : port, input data : "1" input). At forced reset,

the status registers (the SCnBRKF flag of the SCnMD2 register, all flags of the SCnMD3 register) are

initialized as they are set at reset, but the control register holds the setting value.

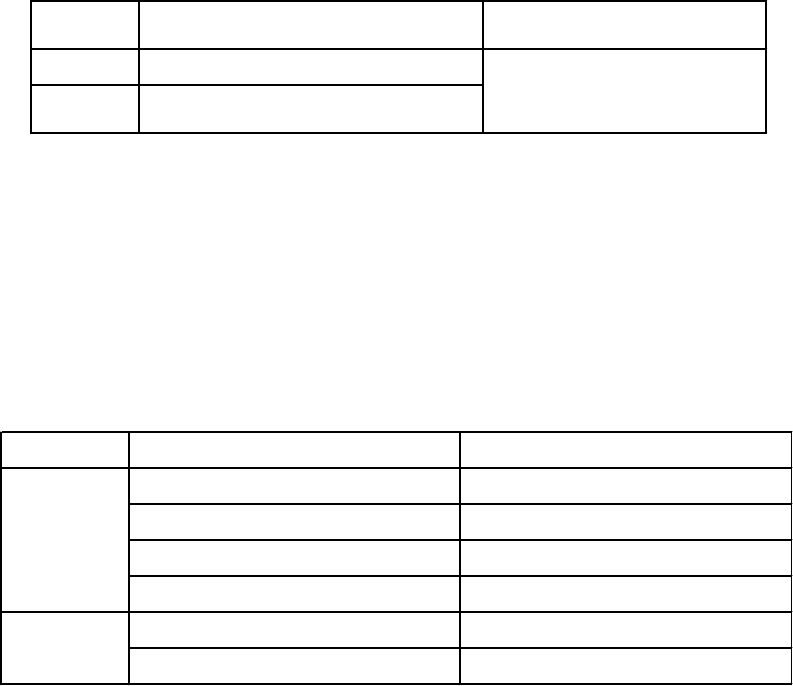

Table 11-3-4 Last Bit Data Length of Transfer Data

Other Control Flag Setup

Table 11-3-5 shows flags that are not used at clock synchronous communication. So, they are not

needed to set or monitor.

Table 11-3-5 Other Control Flag

Last Bit of Transfer Data

Table 11-3-4 shows the data output holding period of the last bit at transmission, and the minimum data

input period of the last bit at reception. After data output holding period of the last bit, "H" is output.

The last bit data holding period at

transmission

The last data input period at

reception

At master 1 bit data length

At s lave

[1 bit data length of external clock x 1/2] +

[internal clocl frequency x (1/2 to 3/2)]

1 bit data length (Minimum)

Register Flag Detail

SCnBRKF Brake status reception monitor

SCnNPE Parity is enabled

SCnPM1 to 0 Added bit specification

SCnFM1 to 0 Frame mode specification

SCnPEK Parity error detection

SCnFEF Frame error detection

SCnMD3

SCnMD2