XIV - 3

Chapter 14 Automatic Transfer Controller

Overview

13

14-1-2 Functions

Table 14-1-1 and 14-1-2 provide a list of the ATC1 trigger factors and transfer modes.

ATC1 Trigger Factors

ATC Transfer Modes

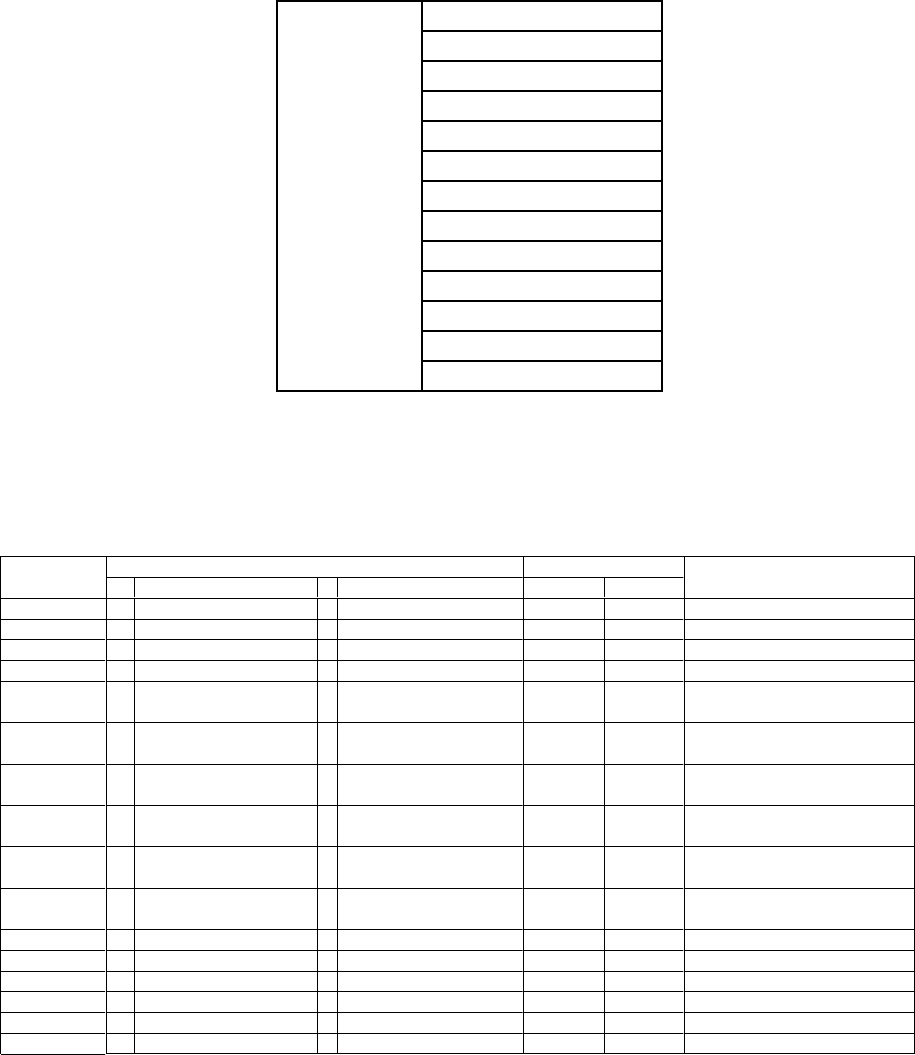

Table 14-1-1 ATC1 Trigger Factors

Table 14-1-2 Transfer Modes

Transfer Mode

Transfer Direction (*)

Pointer Increment Control

Transfer Operation

Cycle

Source Address → Destination Address AT1MAP0 AT1MAP1

Transfer mode 0

AT1MAP0 →

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

→

AT1MAP1 (I/O area) -

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

1-byte data transfer

Transfer mode 1 AT1MAP1 (I/O area) AT1MAP0 1-byte data transfer

Transfer mode 2 AT1MAP0 AT1MAP1 (I/O area) AT1MAP0+1 1-byte data transfer

Transfer mode 3 AT1MAP1 (I/O area) AT1MAP0 AT1MAP0+1 1-byte data transfer

Transfer mode 4

1st AT1MAP0 AT1MAP1 (I/O area : even ADR) AT1MAP0+1 1-word data transfer

2nd AT1MAP0 [=AT1MAP0+1] AT1MAP1 (I/O area : odd ADR) AT1MAP0+1

(An even address must be set in AT1MAP1)

Transfer mode 5

1st AT1MAP1 (I/O area : even ADR) AT1MAP0 AT1MAP0+1 1 word data transfer

2nd AT1MAP1 (I/O area : odd ADR) AT1MAP0 [=AT1MAP0+1] AT1MAP0+1

Transfer mode 6

1st AT1MAP1 (I/O area) AT1MAP0 AT1MAP0+1 Two 1-byte data tranfers

2nd AT1MAP0 [=AT1MAP0+1] AT1MAP1 (I/O area) AT1MAP0+1

Transfer mode 7

1st AT1MAP1 (I/O area) AT1MAP0 AT1MAP0+1 Two 1-byte data tranfers

2nd AT1MAP0 [=AT1MAP0+1] AT1MAP1 (I/O area)

Transfer mode 8

1st AT1MAP1 (I/O area : even ADR) AT1MAP0 AT1MAP0+1 Two 1-byte data tranfers

2nd AT1MAP0 [=AT1MAP0+1] AT1MAP1 (I/O area : odd ADR) AT1MAP0+1

Transfer mode 9

1st AT1MAP1 (I/O area : even ADR) AT1MAP0 AT1MAP0+1 Two 1-byte data tranfers

2nd AT1MAP0 [=AT1MAP0+1] AT1MAP1 (I/O area : odd ADR)

Transfer mode A AT1MAP0 AT1MAP1 1-byte data transfer (whole memory area)

Transfer mode B AT1MAP1 AT1MAP0 1-byte data transfer (whole memory area)

Transfer mode C AT1MAP0 AT1MAP1 AT1MAP0+1 AT1MAP1+1 1-word data transfer (whole memory area)

Transfer mode D AT1MAP1 AT1MAP0 AT1MAP0+1 AT1MAP1+1 1-word data transfer (whole memory area)

Transfer mode E AT1MAP0 AT1MAP1 AT1MAP0+1 AT1MAP1+1 Burst transfer ( continues until AT1TCR=0)

Transfer mode F AT1MAP1 AT1MAP0 AT1MAP0+1 AT1MAP1+1 Burst transfer ( continues until AT1TCR=0)

(*) When a memory pointer points to the I/O space, only the lower 8 bits of the pointer are valid.

(An even address must be set in AT1MAP1)

(An even address must be set in AT1MAP1)

(An even address must be set in AT1MAP1)

External interrupt 0

External interrupt 1

External interrupt 2

External interrupt 3

Serial interface 4 interrupt

Timer 1 interrupt

Timer 7 interrupt

Timer 7 capture trigger

Serial interface 0 interrupt

Serial interface1 interrupt

Serial interface 3 interrupt

A/D converter interrupt

Software activation

Trigger Factors