VIII - 9

Chapter 8 Time Base Timer / 8-bit Free-running Timer

8-bit Free-running Timer

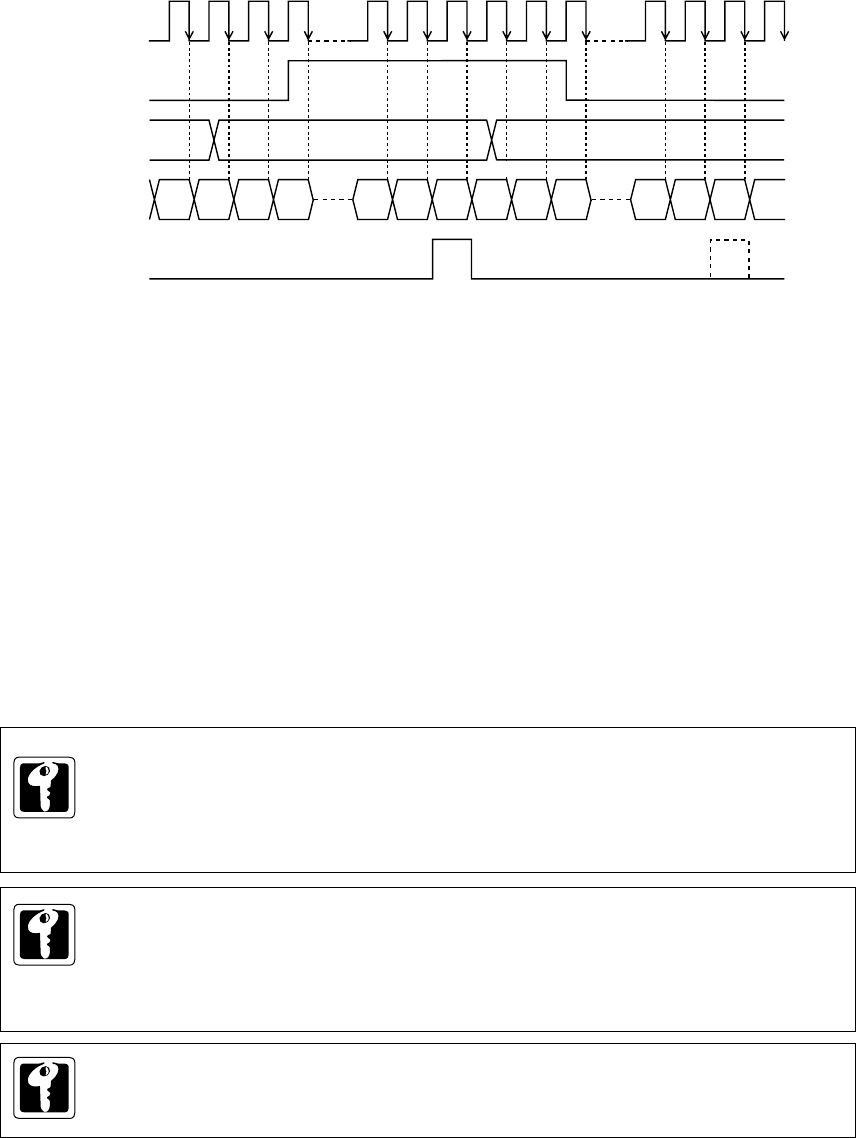

Count Timing of Timer Operation (Timer 6)

Binary counter counts up with the selected clock source as a count clock.

(A) When any data is written to the compare register as the TM6CLRS flag is "0", the binary

counter is cleared to x'00'.

(B) Even if any data is written to the compare register as the TM6CLRS flag is "1", the binary

counter is not changed.

(C) When the binary counter reaches the value of the compare register as the TM6CLRS flag is

"1", an interrupt request flag is set at the next count clock.

(D) When an interrupt request flag is set, the binary counter is cleared to x'00' and restarts the

counting.

(E) Even if the binary counter reaches the value of the compare register as the TM6CLRS flag is

"0", no interrupt request flag is set.

Figure 8-3-2 Count Timing of Timer Operation (Timer 6)

M

NM

01

01 02 N-1

N02/00

00 01

Count clock

TM6CLRS

flag

Compare

register

Binary

counter

Interrupt

request

flag

02 03 M-1

M

00 01

(A)

(C)

(D)

(B)

(E)

If the compare register is set the smaller than the binary counter during the count operation,

the binary counter counts up to the overflow, at first.

If fx is selected as the count clock source in timer 6, when the binary counter is read at

operation, uncertain value on counting up may be read. To prevent this, select the synchro-

nous fx as the count clock source.

But if the synchronous fx is selected as the count clock source, CPU mode cannot return

from STOP/HALT mode.

When the binary counter reaches the value in the compare register, the inrerrupt request flag

is set and the binary counter is cleared, at the next count clock.

So, set the compare register as :

Compare register setting = (count till the interrupt request - 1)