Chapter 3 Interrupts

III - 16

Control Registers

3-2-2 Interrupt Control Registers

The interrupt control registers include the maskable interrupt control registers (xxxICR) and the non-

maskable interrupt control register (NMICR).

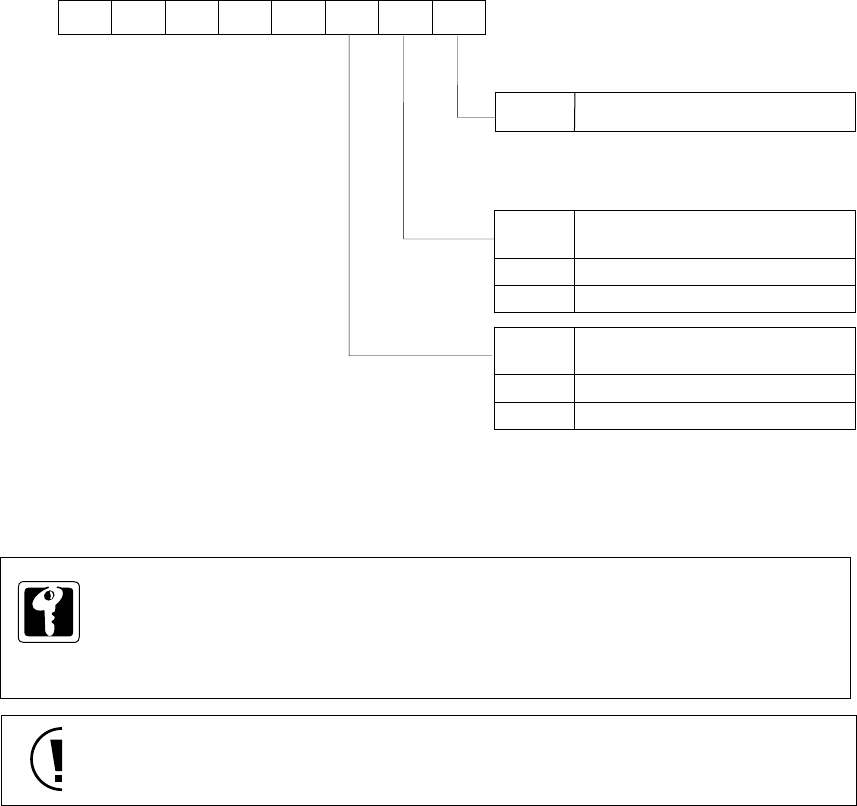

■Non-Maskable Interrupt Control Register (NMICR address: x'03FE1')

The non-maskable interrupt control register (NMICR) stores the non maskable interrupt request. When

the non-maskable interrupt request is generated, the interrupt is accepted regardless of the interrupt

mask level (IMn) of PSW. The hardware then branches to the address stored at location x'04004' in the

interrupt vector table. The watchdog timer overflow interrupt request flag (WDIR) is set to "1" when the

watchdog timer overflows. The program interrupt request flag (PIR) is set to "1" when the undefined

instruction is executed.

WDIR

Watchdog interrupt request flag

0

Interrupt request generated

7

0

NMICR

WDIR Reserved

(At reset : -----000)

1

No interrupt request

PIR

PIR

Program interrupt request flag

0

Interrupt request generated

1

No interrupt request

1

2

34

5

6

Reserved

Always set to "0".

-

-

-- -

Figure 3-2-1 Non-Maskable Interrupt Control Register

(NMICR:x'03FE1', R/W)

On this LSI, when undefined instruction is decoded, the program interrupt request flag (PIR)

is set to "1", and the non-maskable interrupt is generated.

If the PIR flag setup is confirmed by the non-maskable interrupt service routine, the reset via

the software is recommended, When software reset, the reset pin (p27) outputs "0".

Once the WDIR flag becomes "1" after non-maskable interrupt happens, only the program

can clear it to "0".