Chapter 14 Automatic Transfer Controller

Operation

XIV - 16

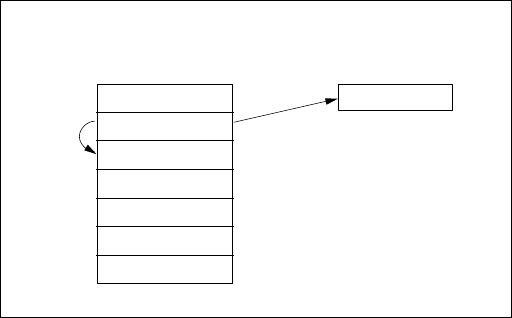

Figure 14-3-4 Transfer Mode 2

Set the source address in 18-bit memory pointer 0 (AT1MAP0H, M, L), and set the destination I/O

address in lower 8 bits of memory pointer 1(AT1MAP1L). The upper 10 bits of the I/O space address

(x'03F') need not to be set in AT1MAP1H and AT1MAP1M.

In transfer mode 2, the value in memory pointer 0 increments by 1 each time a byte-length data transfer

ends. As a result, the source address for the next transfer is one address higher than that for the

previous transfer.

Set the data transfer count for ATC1 in the transfer data counter (AT1TRC). The counter can be set to a

maximum of 255 transfers. The counter decrements each time ATC1 is activated. When it reaches x'00',

an interrupt (ATC1IRQ) occurs and the automatic transfer ends.

(1)

(2)

AT1MAP0

AT1MAP0 + 1

AT1MAP0 + 2

AT1MAP0 + 3

AT1MAP1

Memory Pointer 0

00000 - 3FFFF 03F00 - 03FFF

Memory Pointer 1

(Only lower

8 bits are valid)

14-3-7 Transfer Mode 2

In transfer mode 2, ATC1 automatically transfers one byte of data from any memory space to the I/O space

(special registers : x'03F00' - x'03FFF') every time an ATC1 activation request occurs.