III - 3

Chapter 3 Interrupts

Overview

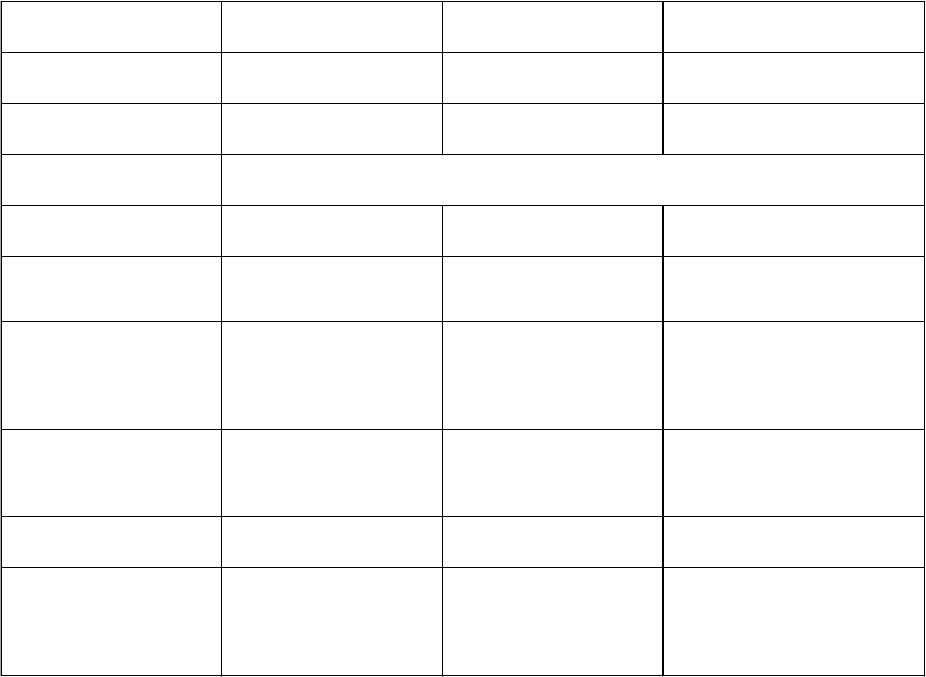

Table 3-1-1 Interrupt Functions

3-1-1 Functions

3

Interrupt type Reset (interrupt) Non-maskable interrupt Maskable interrupt

Vector number 0 1 2 to 28

Table address x'04000' x'04004' x'04008' to x'04070'

Starting address

Level 0 to 2

(set by software)

Errors detection, External pin input

Internal peripheral

function

Input interrupt request

Input to CPU core from

level set in interrupt level flag

non-maskable interrupt

(xxxL Vn) of maskable

control register (NMICR) interrupt control register

(xxxICR) to CPU core.

Acceptance only by the

interrupt control of the register

(xxxICR) and the interrupt

mask level in PSW.

Machine cycles until

acceptance

12 12 12

Values of the interrupt level

All flags are cleared The interrupt mask level flag (xxxLVn) are set to the

to "0". flag in PSW is cleared interrupt mask level (masking

to "00". all interrupt requests with the

same or the lower priority.)

PI interrupt

Address specified by vector address

Interrupt level - -

Generated operation Direct input to CPU core

Interrupt factor External RST pin input

PSW status after acceptance

Accept operation Always accepts Always accepts