Chapter 17 Appendices

XVII - 12

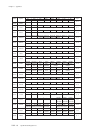

Special Function Registers List

Bit Symbol /Initial Value /Description

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

X'3FAE'

X'3FAF'

X'3FB0'

X'3FB1'

X'3FB2'

Address Register Page

- ----SC3ODC1 SC3ODC0

SC3ODC

P52

Output Type

Selection

P51

Output Type

Selection

XII - 9

-----SC3PSC2 SC3PSC1 SC3PSC0

SC3CKS

Serial 3 Transfer Clock Selection

(Prescaler Output)

XII - 9

V - 10

ANSH1 ANSH0 ANCK1 ANCK0 ANLADE - - -

ANCTR0

A/D Sample Hold

Timer Setup

A/D Conversion Clock

Selection

A/D Rudder

Resistance

Control

XV - 5

- - - - Reserved ANCHS2 ANCHS1 ANCHS0

ANCTR1

Analog Input Channel Selection

XV - 6

ANST ANSTSEL -

-

----

ANCTR2

A/D Conversion

Status

A/D Conversion

Start Factor

Selection

XV - 6

Set Always

to "0"

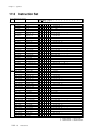

X'3FB3'

X'3FB4'

ANBUF07 ANBUF06 ------

X'3FC7'

ANBUF0

A/D Conversion Data Storage

Register (Lower 2 bits)

XV - 7

ANBUF17 ANBUF16 ANBUF15 ANBUF14 ANBUF13 ANBUF12 ANBUF11 ANBUF10

X'3FC8'

ANBUF1

A/D Conversion Data Storage

Register (Upper 8 bits)

XV - 7

X'3FC9'

RC0APL7 RC0APL6 RC0APL5 RC0APL4 RC0APL3 RC0APL2 RC0APL1 RC0APL0

RC0APL

ROM Correction Address 0 Setting Register Lower 8 bits

II - 33

RC0APM7 RC0APM6 RC0APM5 RC0APM4 RC0APM3 RC0APM2 RC0APM1 RC0APM0

RC0APM

ROM Correction Address 0 Setting Register Middle 8 bits

II - 33

------RC0APH1 RC0APH0

ROM Correction Addreess 0 Setting Register Upper 2 bits

II - 33RC0APH

X'3FBE'

X'3FBF'

DABUSY DACH1 DACH0

DACTR

D/A Conversion

Enable Flag

PA1

Output Type

Selection

PA0

Output Type

Selection

XVI - 5

DA01BUF7 DA01BUF6 DA01BUF5 DA01BUF4 DA01BUF3 DA01BUF2 DA01BUF1 DA01BUF0

DADR01

D/A Conversion Data Storage Register

XVI - 6

--

-

-

-

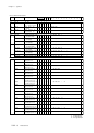

X'3FCB'

X'3FCC'

X'3FCD'

X'3FCE'

X'3FCF'

X'3FD0'

RC1APM7 RC1APM6 RC1APM5 RC1APM4 RC1APM3 RC1APM2 RC1APM1 RC1APM0

RC1APM

ROM Correction Address 1 Setting Register Middle 8 bits

II - 33

------RC1APH1 RC1APH0

ROM Correction Addreess 1 Setting Register Upper 2 bits

II - 33RC1APH

RC2APL7 RC2APL6 RC2APL5 RC2APL4 RC2APL3 RC2APL2 RC2APL1 RC2APL0

RC2APL

ROM Correction Address 2 Setting Register Lower 8 bits

II - 34

RC2APM7 RC2APM6 RC2APM5 RC2APM4 RC2APM3 RC2APM2 RC2APM1 RC2APM0

RC2APM

ROM Correction Address 2 Setting Register Middle 8 bits

II - 34

------RC2APH1 RC2APH0

ROM Correction Addreess 2 Setting Register Upper 2 bits

II - 34RC2APH

FMODE AT1ACT ATMD3 ATMD2 ATMD1 ATMD0 Reserved AT1EN

ATCNT0

Pointer 0

Increment

Control

ATC1 Program

Activation Flag

ATC1 Data Transfer Mode Selection

Set Always

to "0"

ATC1 Transfer

Enable

XIV - 6

X'3FCA'

RC1APL7 RC1APL6 RC1APL5 RC1APL4 RC1APL3 RC1APL2 RC1APL1 RC1APL0

RC1APL

ROM Correction Address 1 Setting Register Lower 8 bits

II - 33

Reserved

Set Always

to "0"