II - 9

Chapter 2 CPU Basics

Overview

Zero Flag (ZF)

Zero flag (ZF) is set to "1", when all bits are '0' in the operation result. Otherwise, zero flag is cleared to

"0".

Carry Flag (CF)

Carry flag (CF) is set to "1", when a carry from or a borrow to the MSB occurs. Carry flag is cleared to

"0", when no carry or borrow occurs.

Negative Flag (NF)

Negative flag (NF) is set to "1" when MSB is '1' and reset to "0" when MSB is '0'. Negative flag is used

to handle a signed value.

Overflow Flag (VF)

Overflow flag (VF) is set to "1", when the arithmetic operation results overflow as a signed value. Other-

wise, overflow flag is cleared to "0".

Overflow flag is used to handle a signed value.

Interrupt Mask Level (IM1 and IM0)

Interrupt mask level (IM1 and IM0) controls the maskable interrupt acceptance in accordance with the

interrupt factor interrupt priority for the interrupt control circuit in the CPU. The two-bit control flag

defines levels '0' to '3'. Level 0 is the highest mask level. The interrupt request will be accepted only

when the level set in the interrupt level flag (xxxLVn) of the interrupt control register (xxxICR) is higher

than the interrupt mask level. When the interrupt is accepted, the level is reset to IM1-IM0, and interrupts

whose mask levels are the same or lower are rejected during the accepted interrupt processing.

Maskable Interrupt Enable (MIE)

Maskable interrupt enable flag (MIE) enables/disables acceptance of maskable interrupts by the CPU's

internal interrupt acceptance circuit. A '1' enables maskable interrupts; a '0' disables all maskable inter-

rupts regardless of the interrupt mask level (IM1-IM0) setting in PSW.

This flag is not changed by interrupts.

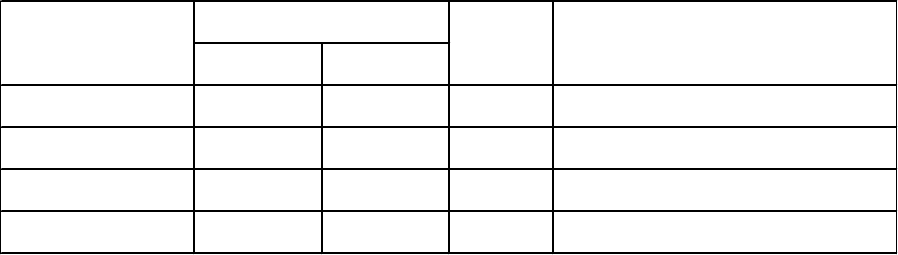

Table 2-1-3 Interrupt Mask Level and Interrupt Acceptance

IM1 IM0

Mask level 0 0 0 High Non-maskable interrupt (NMI) only

Mask level 1 0 1 . NMI, Level 0

Mask level 2 1 0 . NMI, Level 0 to 1

Mask level 3 1 1 Low NMI, Level 0 to 2

Interrupt mask level

Priority Acceptable interrupt levels