Chapter 2 CPU Basics

II - 40

Reset

7

0

1/2

15

to 1/2

20

R R

internal reset release

WDIRQ

S

1/2 to 1/2

14

R

MUX

fs/2

14

fs/2

6

fs/2

12

fs/2

4

fs/2

10

fs/2

8

fs/2

2

HALT

fs

(sysclk)

MUX

fs/2

20

fs/2

22

fs/2

18

fs/2

16

WDCTR

WDTS1

-

WDTC0

WDTC1

WDTC2

-

WDTS0

WDEN

7

0

DLYCTR

DLYS1

DLYS2

BUZS0

BUZS1

BUZS2

BUZOE

DLYS0

-

NRST

STOP

writeWDCTR

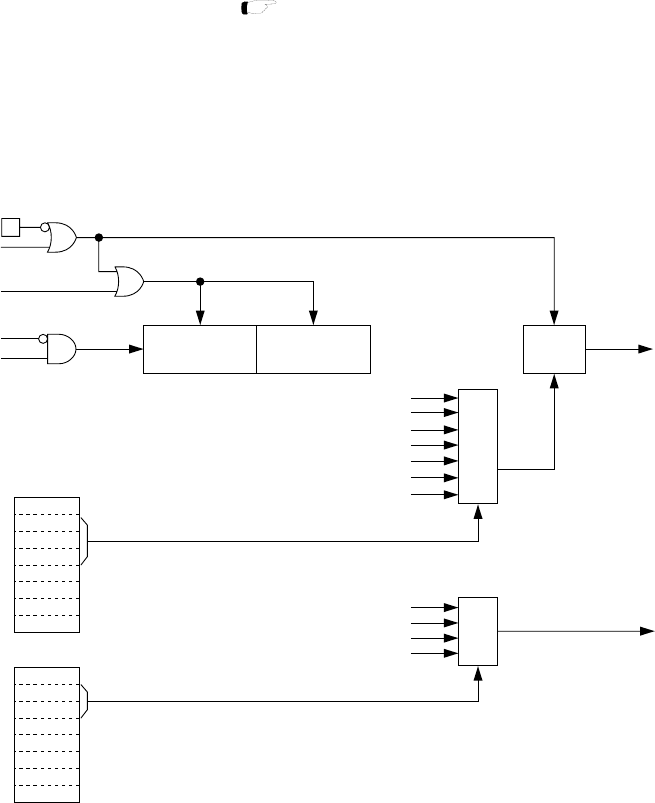

2-8-2 Oscillation Stabilization Wait time

Oscillation stabilization wait time is the period from the stop of oscillation circuit to the stablization for

oscillation. Oscillation stabilization wait time is automatically inserted at releasing from reset and at

recovering from STOP mode. At recovering from STOP mode the oscillation stabilization wait time con-

trol register (DLYCTR) is set to select the oscillation stabilization wait time. At releasing from reset,

oscillation stabilization wait time is fixed.

The timer that counts oscillation stabilization wait time is also used as a watchdog timer. That is used as

a runaway detective timer at anytime except at releasing from reset and at recovering from STOP mode.

Watchdog timer is initiated at reset and at STOP mode and starts counting from the initialize value

(x'0000') when system clock (fs) is as clock source. After oscillation stabilization wait time, it continues

counting as a watchdog timer. [ Chapter 9 Watchdog timer ]

Block Diagram of Oscillation Stabilization Wait Time (watchdog timer)

Figure 2-8-3 Block Diagram of Osillation Stabilization Wait Time (watchdog timer)