Chapter 11 Serial Interface 0, 1

XI - 46

Operation

Judgement of Break Status Reception

Reception at break status can be judged. If all received data from start bit to stop bit is "0", the SCnBRKF

flag of the SCnMD2 register is set and regard the break status. The SCnBRKF flag is set at generation

of the reception complete interrupt SCnRIRQ.

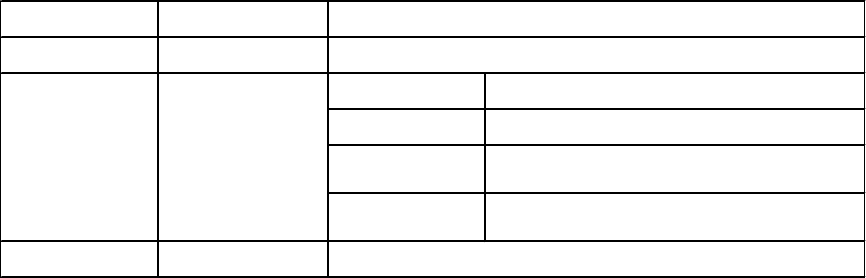

Table 11-3-21 Reception Error Source of UART Serial Interface

Sequence Communication

It is possible to transfer continuously. If data is set to the transmission data buffer TXBUFn during

communication, the transmission buffer empty flag SCnTEMP is set to continue the communication,

automatically. In this case, there is no pause on communication. Data should be set to TXBUFn after

data is loaded to the inside shift register before the communication complete interrupt SC0TIRQ is

generated.

Also, this LSI has an automatic data transfer function ATC1 that can be one of an activation factor. At

activation by ATC1, data can be transfered up to 255 bytes, continuously. In this case, there is a commu-

nication blank ; up to 18 machine cycles + 3.5 bit data length. For an activation by ATC1, refer to chapter

15. automatic transfer controller, transfer mode 6 to 9.

Reception Error

At reception , there are 3 types of error ; overrun error, parity error and framing error. Reception error can

be determined by the SCnORE, SCnPEK, SCnFEF flag of the SCnMD3 register. Even one of those

errors is detected, the SCnERE flag of the SCnMD3 register is set to "1". The SCnPEK, the SCnFEF

flags in recepption error flag are renewed at generation of the reception complete interrupt SCnRIRQ.

The SCnORE flag is holded the status unless data of RXBUFn is read out. The judgements of the

received error flag should be operated until the next communication is finished. The communication

operation does not have any effect on those error flags . Table 11-3-21 shows the list of reception error

source.

Flag Error

SCnORE Overrun error

at fixed to 0 when parity bit is "1"

at fixed to 1 when parity bit is "0"

odd parity

The total of "1" of parity bit and character bit is

even.

even parity

The total of "1" of parity bit and character bit is

odd.

SCnFEF Framing error Stop bit is not detected.

Error source

Next data is received before reading the receive buffer.

SCnPEK Parity error