IX - 5

Chapter 9 Watchdog Timer

Operation

8

WDTS1 WDTS0 Watchdog time-out period

00 2

16

Xsystemclock

01 2

18

Xsystemclock

10 2

20

Xsystemclock

11 2

22

Xsystemclock

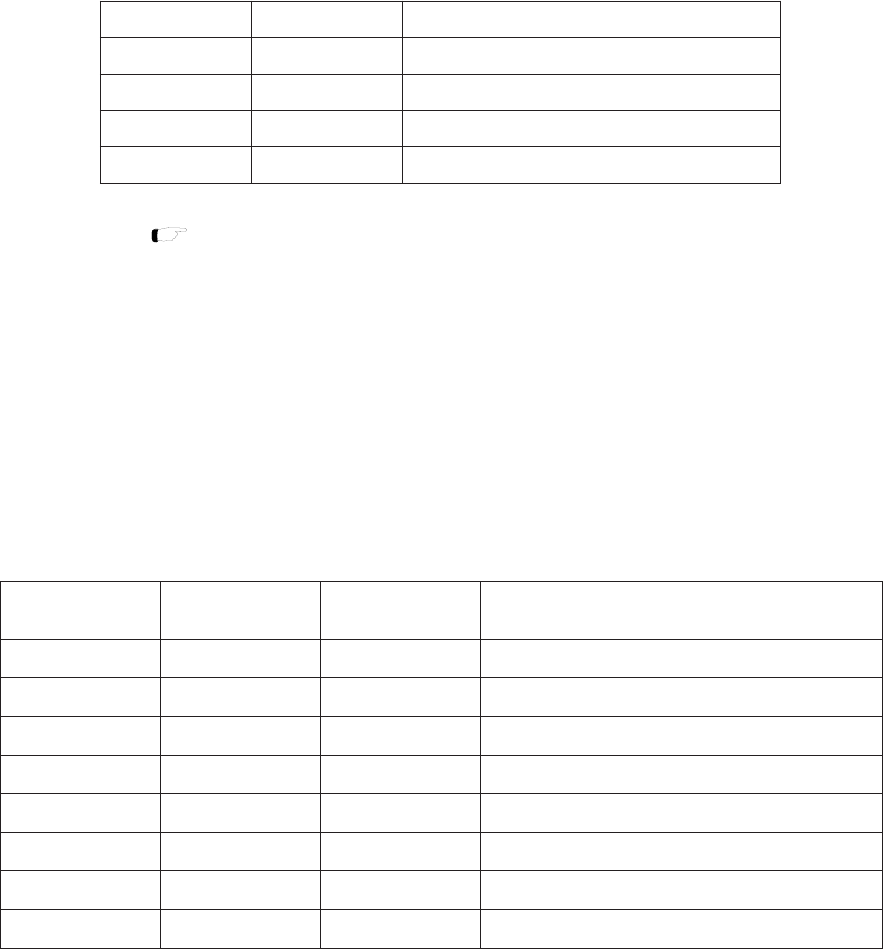

Watchdog Timer Period

The watchdog timer period is decided by the bp2, 1 (WDTS1-0) of the watchdog timer control register

(WDCTR) and the system clock (fs). If the watchdog timer is not cleared till the set period of watchdog

timer, that is regarded as an error and the watchdog interrupt (WDIRQ) of the non-maskable interrupt

(NMI) is generated.

2CTDW1CTDW0CTAW

ehttaderaelcebnacremitgodhctaW

eromroelcycgniwollof

000 timilon

001 2

7

Xkcolcmetsys

010 2

9

Xkcolcmetsys

011 2

11

Xkcolcmetsys

100 2

31

Xkcolcmetsys

10 1 2

51

Xkcolcmetsys

110 2

71

Xkcolcmetsys

111 2

91

Xkcolcmetsys

How to Clear Watchdog Timer

The watchdog timer can be cleared by writing to the watchdog timer control register (WDCTR). The

watchdog timer can be cleared regardless of the writing data to the register. The bit-set (BSET) that does

not change the value is recommended.

The watchdog timer period is generally decided from the execution time for main routine of program.

That should be set the longer period than the value of the execution time for main routine divided by

natural number (1, 2, , , ). And insert the instruction of the watchdog timer clear to the main routine as that

value makes the same cycle.

The Lowest Value for Watchdog Timer Clear

The lowest value for watchdog timer clear is decided by the bp5, 4, 3 (WDTC2, WDTC1, WDTC0) of the

watchdog timer control register (WDCTR).

Table 9-3-2 The Lowest Value for Watchdog Timer Clear

System clock is decided by the CPU mode control register (CPUM).

[

Chapter 2 2-5. Clock Switching ]

Table 9-3-1 Watchdog Timer Period