V - 11

Chapter 5 Prescaler

Operation

5-3 Operation

5-3-1 Operation

Prescaler Operation (Prescaler 0 to 1)

Prescaler 0 is a 7-bit and prescaler 1 is a 3-bit free-running counter that divides the base clock. This

prescaler can be started or stopped by the PSCEN flag of the prescaler control register (PSCMD).

Count Timing of Prescaler Operation (Prescaler 0 and 1)

Prescaler 0 counts up at the falling edge of fosc.

Prescaler 1 counts up at the falling edge of fs.

Peripheral Functions with Prescaler Output Cycle Clock

Table 5-3-1 shows the prescaler output clock source that the peripheral functions can be used, and the

registers that control the clock source selection.

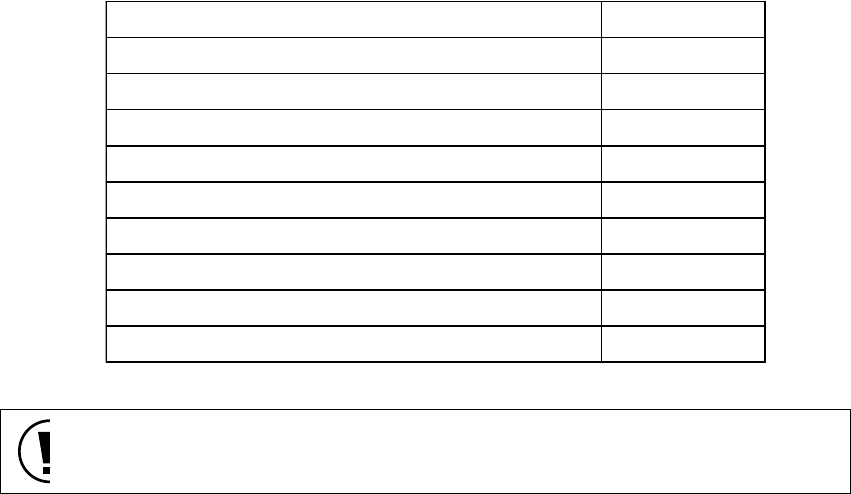

Table 5-3-1 Peripheral Functions Used with Prescaler Output Cycle Clock

When the prescaler output clock source is used, counting of prescaler should be enabled

before starting the peripheral functions.

Control register

External interrupt 0 Noise filter sampling clock -

External interrupt 1 Noise filter sampling clock -

Timer 0 Count clock CK0MD

Timer 1 Count clock CK1MD

Timer 4 Count clock CK4MD

Timer 5 Count clock CK5MD

Serial 0 Transfer clock SC0CKS

Serial 1 Transfer clock SC1CKS

Serial 3 Transfer clock SC3CKS

Peripheral functions