Chapter 7 16-bit Timer

VII - 10

16-bit Timer Count

7-3 16-bit Timer Count

7-3-1 Operation

The timer operation can constantly generate interrupts.

16-bit Timer Operation (Timer 7)

The generation cycle of an timer interrupt is set by the clock source selection and the set value of the

compare register 1 (TM7OC1), in advance. When the binary counter (TM7BC) reaches the set value of

the compare register 1, the timer 7 interrupt request is generated at the next count clock. There are 2

sources ; the TM7OC1 compare match or the full count over flow, to be selected to clear the binary

counter. After the binary counter is cleared to x'0000, the counting up is restarted from x'0000'.

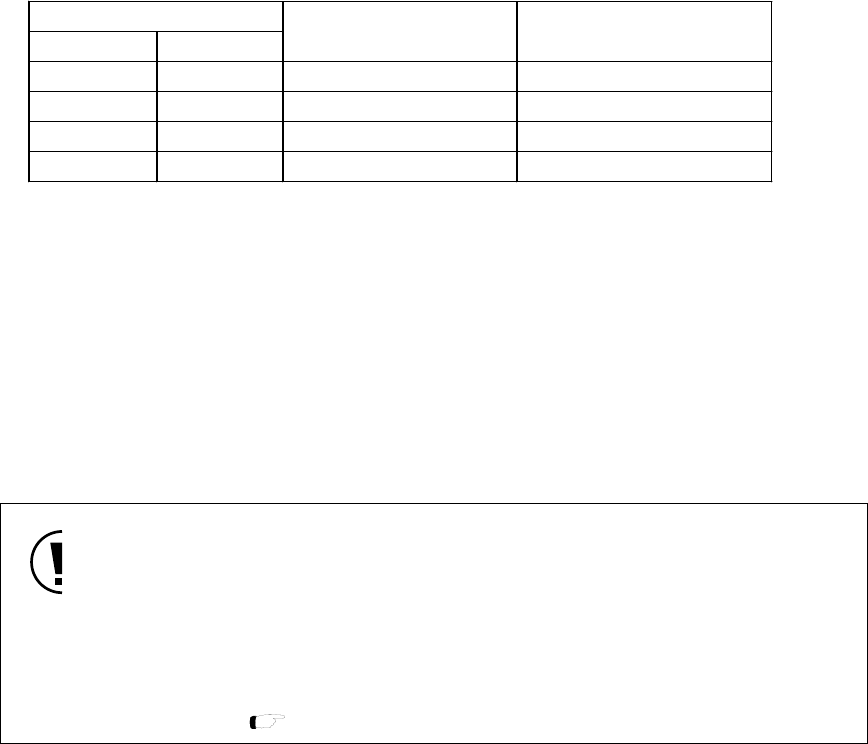

Table 7-3-1 16-bit Timer Interrupt Source and Binary Counter Clear Source (Timer 7)

Timer 7 can generate another set of an independent interrupt (Timer 7 compare register 2 match inter-

rupt) by the set value of the timer 7 compare register (TM7OC2). At that timer, the binary counter is

cleared as the above setup.

The compare register is double buffer type. So, when the value of the preset register is changed during

the counting, the changed value is stored to the compare register as the binary counter is cleared. This

function can change its value of the compare register constantly, without disturbing the cycle during timer

operation (Reload function).

When the CPU reads the 16-bit binary counter (TM7BC), the read data is treated as 8-bits

unit data even if it is a 16-bit MOVW instruction. As a result, it will read the data incorrectly if

a carry from the lower 8 bits to the upper 8 bits occurs during counting.

To read the correct value of the 16-bit counting (TM7BC), use the writing program function to

the input capture register (TM7IC). By writing to the TM7IC, the counting data of TM7BC can

be stored to TM7IC to read out the correct counting data during operation.

[ Chapter 7-9-1. Operation (p.VII-34) ]

TM7IRS1 flag TM7BCR flag

1 1 TM7OC1 compare match TM7OC1 compare match

0 1 TM7OC1 compare match TM7OC1 compare match

1 0 TM7OC1 compare match full count over flow

0 0 full count over flow full count over flow

TM7MD2 register

Interrupt source Binary counter clear source