Chapter 2 CPU Basics

II - 16

Bus Interface

2-3-2 Control Registers

Bus interface is controlled by these 8 bytes of registers : the memory control register (MEMCTR),

memory area control register (AREACTR) and bus mode control register (CSMDn).

Memory Control Register (MEMCTR)

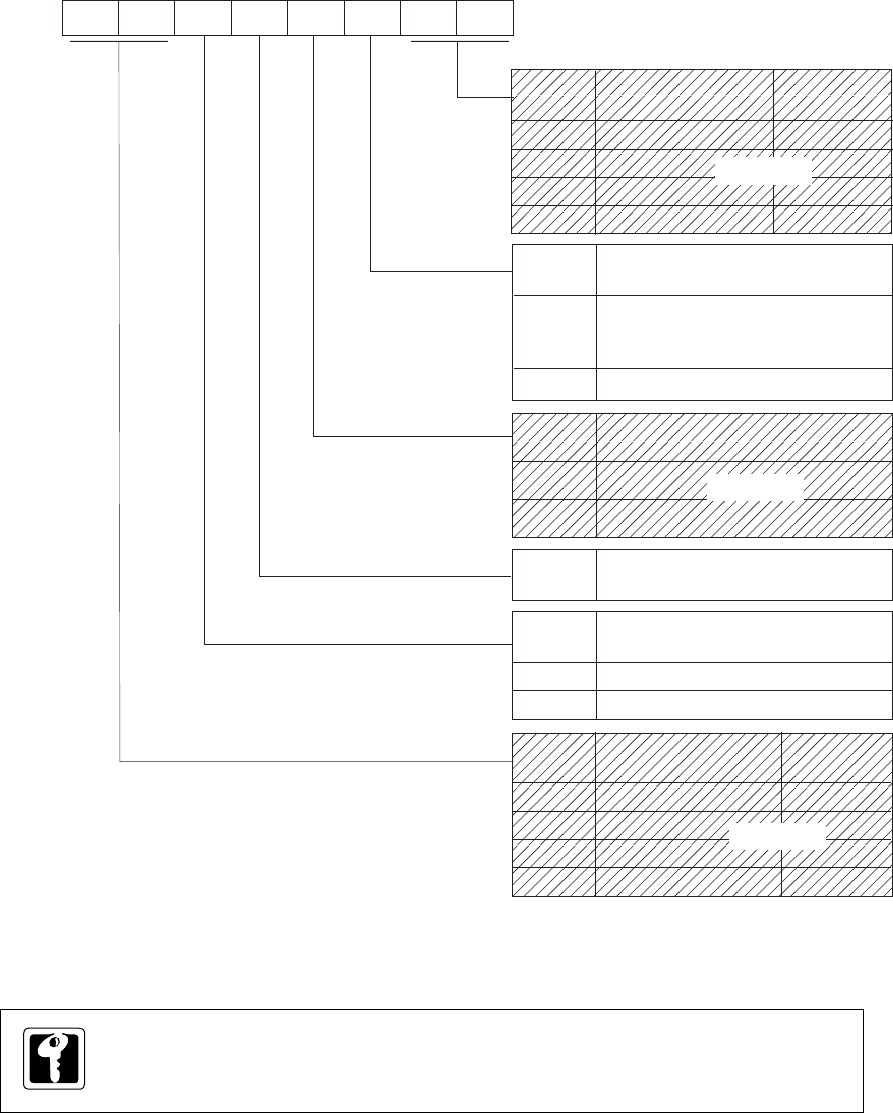

Figure 2-3-2 Memory Control Register (MEMCTR: x'03F01' R/W)

EXW1 to 0, EXWH and IOW1 to 0 flags of the memory control register (MEMCTR) need not

to be set. Set wait cycle with bus mode control register (CSMDn).

70

MEMCTR

EXMEM

IOW1

IOW0

( At reset : 1 1 0 0 1 0 1 1 )

EXWH

EXW1

EXW0

EXW1 to 0 Fixed wait cycles

0 0

0 1

1 0

1 1

No wait cycles

1 wait cycle

2 wait cycles

3 wait cycles

EXWH

Fixed wait cycle mode or handshake mode

0

Handshake mode

Fixed wait cycle mode

1

Bus cycle at

20 MHz oscillation

100 ns

150 ns

200 ns

250 ns

IOW1 to 0

Wait cycles when

accessing special register area

0 0

0 1

1 0

1 1

No wait cycles

1 wait cycle

2 wait cycles

3 wait cycles

Bus cycle at

20 MHz oscillation

100 ns

150 ns

200 ns

250 ns

EXMEM

Set always to "0"

IVBM

IVBM

Base address setting for interrupt vector table

0

Interrupt vector base = x'04000'

Interrupt vector base = x'00100'

1

6431

5

2

IRWE

IRWE

Software write enable flag for interrupt request flag

0

Software write disable

Even if data is written to each interrupt control

register (xxxICR), the state of the interrupt

request flag (xxxIR) will not change.

Software write enable

1

Don't care

Don't care

Don't care